Introduction to Embedded Systems EHB326E Lectures

## Prof. Dr. Müştak E. Yalçın

### Istanbul Technical University

### mustak.valcin@itu.edu.tr

EHB326E (V: 0.1)

# Interface: Ports

- Conducting device on periphery

- Single wire or set of wires with single function

- Connects bus to processor or memory

- Often referred to as a pin

- Actual pins on periphery of IC package that plug into socket on printed-circuit board

- Sometimes metallic balls instead of pins

- Metal "pads" connecting processors and memories within single IC

EHB326E (V: 0.1)

#### port : a city, town, or other place where ships load or unload

#### Prof. Dr. Müstak E. Yalçın (İTÜ)

September, 2018 2 / 18

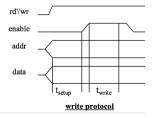

### • Most common method for describing a communication protocol

- Time proceeds to the right on x-axis

- Control signal: low or high

- May be active low (go', go, or go<sub>L</sub>)

- Use terms assert (active) and deassert

- Asserting go' means go=0

- Data signal: not valid or valid

- Protocol may have subprotocols

- Called bus cycle, e.g., read and write

- Each may be several clock cycles

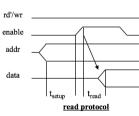

- Read example

- rd'/wr set low, address placed on addr for at least  $t_{setup}$  time before enable asserted.

- enable triggers memory to place data on data wires by time  $t_{read}$

EHB326E (V: 0.1)

**Timing Diagrams**

Interface: Bus

#### Bus

Prof. Dr. Müştak E. Yalçın (İTÜ)

- Set of wires (Uni-directional or bi-directional) with a single function (Address bus, data bus)

- Or, entire collection of wires (Address, data and control)

|           | rd'/wr     |        |

|-----------|------------|--------|

| Processor |            | Memory |

|           | enable     |        |

|           |            |        |

|           | addr[0-11] |        |

|           | 1./50.52   |        |

|           | data[0-7]  |        |

|           | ← / →      |        |

|           |            |        |

|           | bus        |        |

|           | 040        |        |

September, 2018 1 / 18

Prof. Dr. Müştak E. Yalçın (İTÜ)

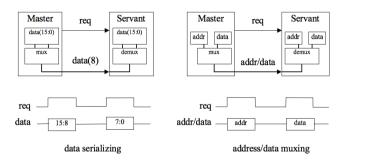

## Basic Protocol

- Actor: master initiates, servant (slave) respond

- actor can be receiver or sender.

- Addresses: special kind of data used to indicate where regular data should go

- Time multiplexing

- Share a single set of wires for multiple pieces of data

- Saves wires at expense of time

Prof. Dr. Müştak E. Yalçın (İTÜ)

September, 2018 5 / 18

- Expansion buses or "slots"

- ISA Industry Standard Architecture

- PCI Personal Component Interconnect

- EISA Extended ISA SIMM Single Inline Memory Module (plugs into slot) DIMM Dual Inline Memory Module (plugs into slot)

EHB326E (V: 0.1)

EHB326E (V: 0.1)

- MCA Micro-Channel Architecture

- AGP Accelerated Graphics Port item VESA Video Electronics Standards Association

- PCMCIA ? Personal Computer Memory Card International AssociaBon (outdated)

- PCI-e PCI express

- HT Hypertransport

#### Disk interfaces

- ATA AT Attachment (named after IBM PC-AT) (outdated)

- IDE Integrated Drive Electronics (same as ATA)

- Enhanced IDE

- SCSI Small Computer Systems Interface

- ESDI Enhanced Small Device Interface

DOMCIA

- PCMCIA

- SATA serial ATA

Ethernet (used for network drives)

- Ethernet (used for network driv

#### External buses

- Parallel sometimes called LPT ("line printer")

- Serial typically RS232C (RS422)

- PS/2 for keyboards and mice

- USB Universal Serial Bus

IrDA Infrared Device Attachment

- FireWire very high speed, developed by IEEE

#### Communications buses

- Parallel/LPT

- Serial/RS232C

- Ethernet

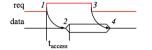

#### Strobe protocol

# Master req Servant

- Master asserts *req* to receive data

- Servant puts data on bus within time *t<sub>access</sub>*

- Master receives data and deasserts *req*

- Servant ready for next request

September, 2018 6 / 18

# Microprocessor interfacing: I/O addressing

A microprocessor communicates with other devices using some of its pins

EHB326E (V: 0.1)

- Port-based I/O (parallel I/O)

- Processor has one or more N-bit ports

- Processor's software reads and writes a port just like a register

▶ 80C51, page 4-7

Prof. Dr. Müştak E. Yalcın (İTÜ)

#### • Bus-based I/O

- Processor has address, data and control ports that form a single bus

- Communication protocol is built into the processor

- A single instruction carries out the read or write protocol on the bus

EHB326E (V: 0.1)

▶ PicoBlaze, page 4-7

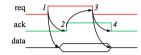

## Handshake protocol

- Master asserts *req* to receive data

- Servant puts data on bus and asserts *ack*

- Master receives data and deasserts *req*

## • Servant ready for next request

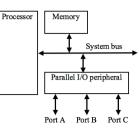

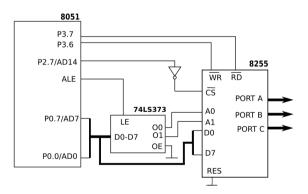

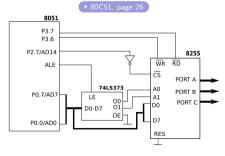

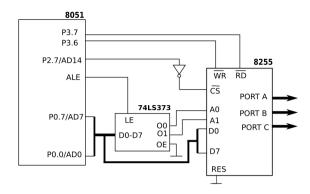

## Parallel I/O peripheral

- When processor only supports bus-based I/O but parallel I/O needed

- Each port on peripheral connected to a register within peripheral that is read/written by the processor

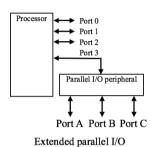

## Extended parallel I/O

- When processor supports port-based I/O but more ports needed

- One or more processor ports interface with parallel I/O peripheral extending total number of ports available for I/O

▶ 8255, Programmable Peripheral Interface

Prof. Dr. Müştak E. Yalçın (İTÜ)

Adding parallel I/O to a busbased I/O processor

September, 2018 9 / 18

The ways to talk to peripherals

- Memory-mapped I/O

- Peripheral registers occupy addresses in same address space as memory

- e.g., Bus has 16-bit address lower 32K addresses may correspond to memory upper 32k addresses may correspond to peripherals

## • Standard I/O (I/O-mapped I/O)

- $\bullet\,$  Additional pin (M/IO) on bus indicates whether a memory or peripheral access

- e.g., Bus has 16-bit address all 64K addresses correspond to memory when M/IO set to 0 all 64K addresses correspond to peripherals when M/IO set to 1

Prof. Dr. Müştak E. Yalçın (İTÜ)

EHB326E (V: 0.1)

September, 2018 10 / 18

I/O port addresses assigned (memory mapped I/O) to ports A, B, C, and the control register:

$\texttt{x1xxxxxx} \texttt{xxxxxx00}{=}4000 \texttt{h}{=}\mathsf{PORT} \texttt{ A}$

$\texttt{x1xxxxxx} \texttt{xxxxxx01}{=}4001 \texttt{h}{=}\mathsf{PORT} \texttt{ B}$

x1xxxxxx xxxxx10=4002h=PORT C

x1xxxxxx xxxxxx11=4003h=CONTROL • 8255, page 3-102 .

EHB326E (V: 0.1)

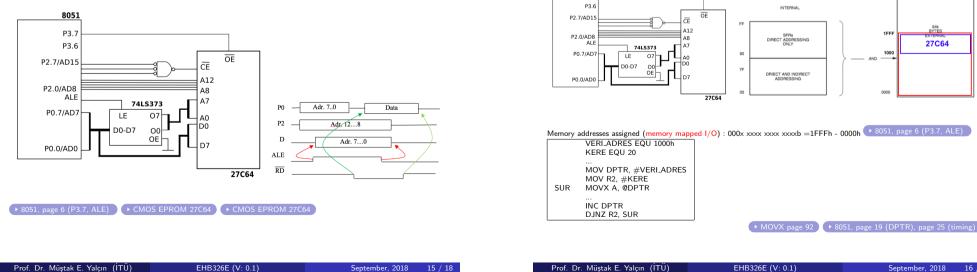

For P3.7 and P3.6 see • 80C51, page 6 and for 74LS373 see • 74LS373

September, 2018

"All the ports of A, B and C are output ports " then the control word of the 8255 for the configurations ( 8255, page 3-100 ) is 1000000b=80h For P3.7 and P3.6 see • 80C51, page 6 and for 74LS373 (Latch) see • 74LS373. A program to send *FFh* to all ports:

| 80h  ightarrow @4003h |

|-----------------------|

| FFh  ightarrow @4000h |

| FFh  ightarrow @4001h |

| FFh  ightarrow @4002h |

Prof. Dr. Müştak E. Yalçın (İTÜ)

EHB326E (V: 0.1) September, 2018 13 / 18

## Memory-mapped I/O

- Requires no special instructions

- Assembly instructions involving memory like MOV and ADD work with peripherals as well • 80C51

- Standard I/O requires special instructions (INPUT, OUTOUT PicoBlaze Page 32) to move data between peripheral registers and memory

## Standard I/O

Prof. Dr. Müstak E. Yalçın (İTÜ)

8051 P3.

- No loss of memory addresses to peripherals

- Simpler address decoding logic in peripherals possible

- When number of peripherals much smaller than address space then high-order address bits can be ignored

EHB326E (V: 0.1)

An external ROM uses the 8051 data space to store the data (starting at 1000H). Write a program to read 20 Bytes of these data.

September, 2018 14 / 18

27C64

EFFE M

166

1000

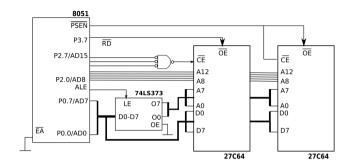

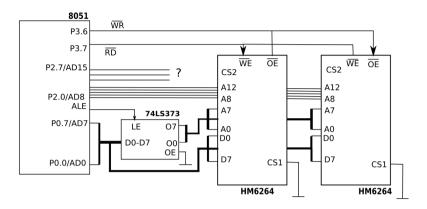

An 8051-based system with 8K bytes of program ROM and 8K bytes of data ROM.

if  $\overline{EA} = 1$ , PC starts from 0000h(internal memory) then 0FFFh (external memory), if  $\overline{EA} = 0$ , PC start from external memory (0000h - ----h).  $\rightarrow$  8051, page 25 (external program memory read cycle)

EHB326E (V: 0.1)

Prof. Dr. Müştak E. Yalçın (İTÜ)

September, 2018 17 / 18

Prof. Dr. Müştak E. Yalçın (İTÜ)

EHB326E (V: 0.1)

September, 2018 18 / 18