#### Programmable Logic Devices (PLDs) PLAs and PALs

- By the late 1970s, standard logic devices were all the rage, and printed circuit boards were loaded with them.

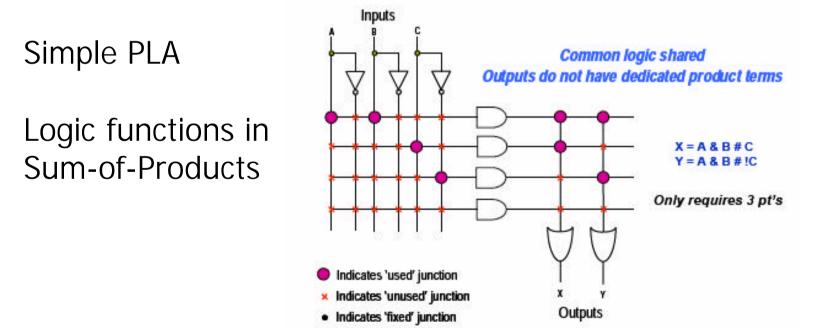

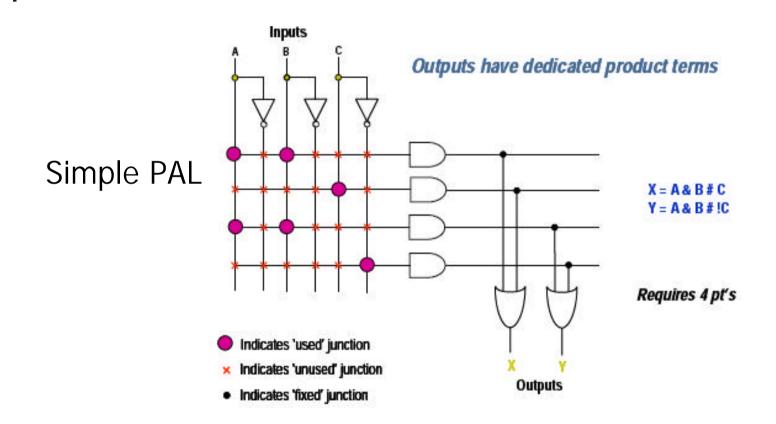

- To offer the ultimate in design flexibility, Ron Cline from Signetics came up with the idea of two programmable planes.

- These two planes provided any combination of "AND" and "OR" gates, as well as sharing of AND terms across multiple ORs.

At the time wafer geometries of 10 µm made the input-to-output delay (or propagation delay) high, which made the devices relatively slow.

- MMI (later purchased by AMD<sup>™</sup>) was enlisted as a second source for the PLA array. After fabrication issues, it was modified to become the programmable array logic (PAL) architecture by fixing one of the programmable planes.

- This new architecture differed from that of the PLA in that one of the programmable planes was fixed – the OR array. PAL architecture also had the added benefit of faster t<sub>PD</sub> and less complex software, but without the flexibility of the PLA structure.

- The architecture had a mesh of horizontal and vertical interconnect tracks.

- At each junction was a fuse. With the aid of software tools, designers could select which junctions would not be connected by "blowing" all unwanted fuses.

- Input pins were connected to the vertical interconnect. The horizontal tracks were connected to AND-OR gates, also called "product terms". These in turn connected to dedicated flip-flops, whose outputs were connected to output pins.

PLDs provided as much as 50 times more gates in a single package than discrete logic devices!

#### Programmable Logic Devices (PLDs) CPLDs and FPGAs

- Altera introduced first CPLD device.

- Complex programmable logic devices (CPLDs) extend the density of SPLDs.

- The concept is to have a few PLD blocks or macrocells on a single device with a generalpurpose interconnect in-between. Simple logic paths can be implemented within a single block.

#### FPGAs & CPLDs CPLD **CPLD** Architecture SPLD Block SPLD Block MC0 MC0 PAL PAL MC1 MC1 I/O or or 1 I/O Interconnect PLA PLA Array MC15 MC15 10 **High Performance** 10 ST XILINX CoolRunner-II DataGATI E XUNX Low Power Lowest Cost CoelCLOCK

- Ease of Design: CPLDs offer the simplest way to implement a design. Once a design has been described, by schematic and/or HDL entry, you simply use CPLD development tools to optimize, fit, and simulate the design.

- Lower Development Costs: CPLDs offer very low development costs. Because CPLDs are re-programmable, you can easily and very inexpensively change, optimize and improve your designs.

More Product Revenue: CPLDs offer very short development cycles, which means your products get to market quicker and begin generating revenue sooner.

Reduced Board Area: CPLDs offer a high level of integration (that is, a large number of system gates per area) and are available in very small form factor packages.

An MPGA (Mask Programmable Gate Array) consists of an array of prefabricated transistors customized for the user's logic circuit by means of wire connections.

Because the silicon foundry performs customization during chip fabrication, the manufacturing time is long, and the user's setup cost is high.

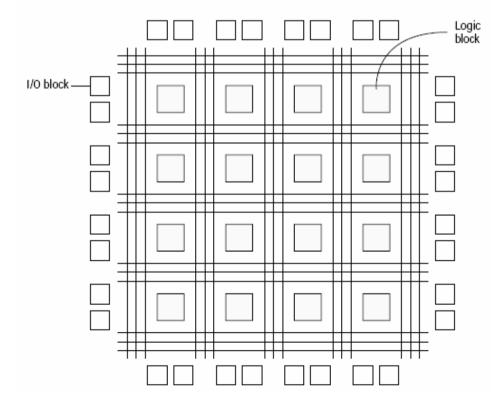

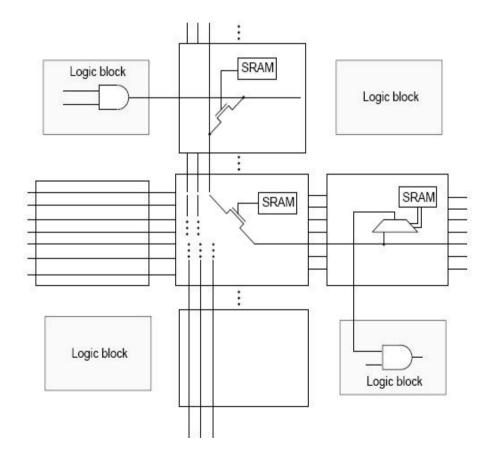

- An FPGA is a regular structure of logic cells (or modules) and interconnect, which is under your complete control. This means that you can design, program, and make changes to your circuit whenever you wish.

- In 1985 Xilinx introduced first FPGA.

- Now FPGAs exceed 10 million gate limit. (Here gate is equivalent to two input AND gate)

FPGA Architecture

Xilinx Virtex 5 550MHz Global Clock Speed

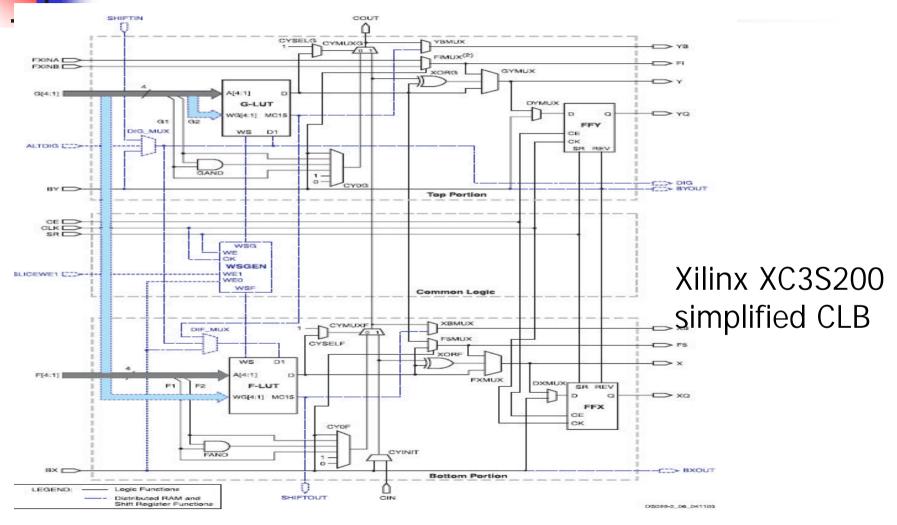

FPGAs contain Configurable Logic Blocks (CLBs) and IO Blocks (IOBs).

CLBs contain main logic resource for implementing synchronous as well as combinational circuits.

There are two basic types of FPGAs: SRAM-based reprogrammable and OTP (One Time Programmable).

These two types of FPGAs differ in the implementation of the logic cell and the mechanism used to make connections in the device.

The dominant type of FPGA is SRAM-based and can be reprogrammed as often as you choose.

In fact, an SRAM FPGA is reprogrammed every time it's powered up, because the FPGA is really a fancy memory chip. That's why you need a serial PROM or system memory with every SRAM FPGA.

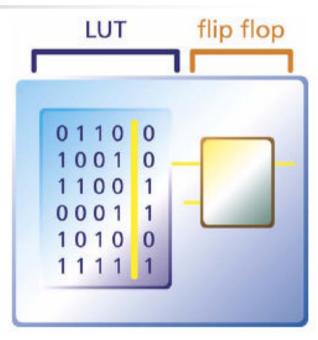

In the SRAM logic cell, instead of conventional gates, an LUT determines the output based on the values of the inputs.

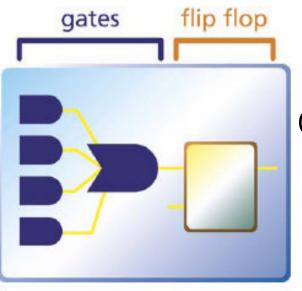

#### **OTP Logic Cell**

SRAM Logic Cell

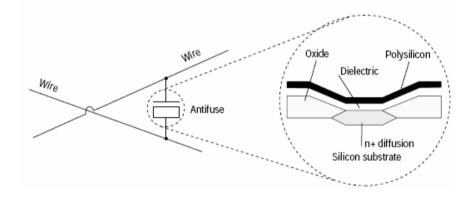

- OTP FPGAs use anti-fuses (contrary to fuses, connections are made, not "blown," during programming) to make permanent connections in the chip.

- OTP FPGAs do not require PROM or other means to download the program to the FPGA.

- However, every time you make a design change, you must throw away the chip! The OTP logic cell is very similar to PLDs, with dedicated gates and flip-flops.

- The first user-programmable switch developed was the fuse used in PLAs.

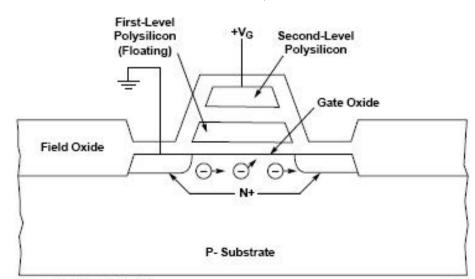

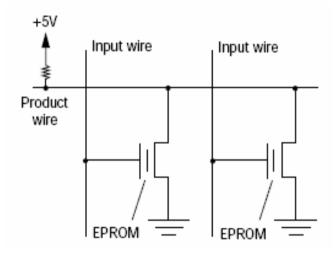

- For CPLDs, the main switch technologies are floating gate transistors like those used in EPROM (erasable programmable read-only memory) and EEPROM (electrically erasable PROM).

- For FPGAs, they are SRAM (static RAM) and antifuse.

| Reprogrammable?  | Volatile?                                                                   | Technology                                                                               |

|------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| No               | No                                                                          | Bipolar                                                                                  |

| Yes              | No                                                                          | UVCMOS                                                                                   |

| (out of circuit) |                                                                             |                                                                                          |

| Yes              | No                                                                          | EECMOS                                                                                   |

| (in circuit)     |                                                                             |                                                                                          |

| Yes              | Yes                                                                         | CMOS                                                                                     |

| (in circuit)     |                                                                             |                                                                                          |

| No               | No                                                                          | CMOS+                                                                                    |

|                  | No<br>Yes<br>(out of circuit)<br>Yes<br>(in circuit)<br>Yes<br>(in circuit) | No No<br>Yes No<br>(out of circuit)<br>Yes No<br>(in circuit)<br>Yes Yes<br>(in circuit) |

#### EPROM Programmable Switches

Bource: ICE, "Memory 1997"

....

From Computer Desktop Encyclopedia © 2004 The Computer Language Co. Inc

#### SRAM Controlled Programmable Switche

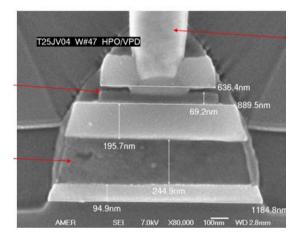

- Antifuses are originally open circuits that take on low resistance only when programmed. Antifuses are manufactured using modified CMOS technology.

- Unprogrammed, the insulator isolates the top and bottom layers; programmed, the insulator becomes a low-resistance link.

# 23-MAR-0

#### Antifuse Structure