# 11-BITS SUB-RANGING ANALOG TO DIGITAL CONVERTER AND SSATOOL

APPROVED BY SUPERVISORY COMMITTEE

Dr. Franco Maloberti, Chair

Dr. Jin Liu

Dr. James R. Hellums

Dr. Murat Torlak

Dr. Andrea Fumagalli

© Copyright by Devrim Yilmaz Aksin 2006

All Rights Reserved

I would like to dedicate this work to my parents,

Nermin and Ibrahim AKSIN.

# 11-BITS SUB-RANGING ANALOG TO DIGITAL CONVERTER AND SSATOOL

by

# DEVRIM YILMAZ AKSIN, B.SC., M.SC.

# DISSERTATION

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY

IN

ELECTRICAL ENGINEERING

# THE UNIVERSITY OF TEXAS AT DALLAS

May 2006

### PREFACE

This dissertation (or thesis or practica report) was produced in accordance with the guidelines which permit the inclusion as part of the dissertation (or thesis or practica report) the text of an original paper, or papers, submitted for publication. The dissertation must conform to all other requirements explained in the "Guide for the Preparation of Master's Theses, Doctoral Dissertations and Doctor of Chemistry Practica Reports at The University of Texas at Dallas." It must include a comprehensive abstract, a full introduction and literature review, and a final overall conclusion. Additional material (procedural and design data as well as descriptions of equipment) must be provided in adequate detail to allow a clear and precise judgment to be made of the importance and originality of the research reported.

It is acceptable for this dissertation (or thesis or practica report) to include as chapters authentic copies of papers already published, provided these meet the type size, margin and legibility requirements. In such cases, connecting texts which provide logical bridges between different manuscripts are mandatory. Where the student is not the sole author of a manuscript, the student is required to make an explicit statement in the introductory material to that manuscript describing the student's contribution to the work and acknowledging the contribution of the other author(s). The signatures of the Supervising Committee which precede all other material in the dissertation (or thesis or practica report) attest the accuracy of this statement.

# ACKNOWLEDGMENTS

I would like to thank to my supervisor Dr. Franco Maloberti for his patience and consistent support, to my committee members Dr. Jin Liu, Dr. James Hellums, Dr. Murat Torlak and Dr. Andrea Fumagalli, and to my long lasting friend Dr. Fikret Dulger. I would like to acknowledge also my colleagues from Texas Instruments Inc., Ross Teggatz, Wayne Chen, Brett Smith and especially Mohammad Al-Shyoukh and Martin Marcus without their help and support life would be much more difficult. Thank you.

December 2005

DEVRIM YILMAZ AKSIN

#### 11-BITS SUB-RANGING ANALOG TO DIGITAL CONVERTER AND SSATOOL

Publication No. \_\_\_\_\_

Devrim Yilmaz Aksin, Ph.D. The University of Texas at Dallas, 2006

#### Supervising Professor: Dr. Franco Maloberti

In this work, an 11-bit Sub-Ranging Analog to Digital converter (ADC) is proposed for power management applications. Designed converter implements all important design specifications of an ADC used in such applications should satisfy, i.e. low power consumption, noise immunity, being able to measure voltage quantities above the power supply voltage such as battery. Proposed ADC can sample voltage quantities above supply voltage using a new bootstrapped sampling switch. A new passive subtractor circuit is also implemented to reduce total silicon area and improve noise performance of the converter. Proposed passive subtractor inherently implements filtering which is very suitable when a DC voltage quantity should be measured in a noisy environment, such as power management systems where high-power switching voltage regulators are generally present. The 11-bit ADC is designed using Texas Instruments LBC7  $0.35 \ \mu m$  technology. Consistent with the application, designed analog-to-digital converter does not contain any sample and hold amplifier, hence it is intended to monitor DC voltage quantities. The conversion time is specified as  $10 \ \mu s$ with an expected duty cycle of 0.1%. The converter draws  $140 \ \mu A$  average current during conversion from 2.75V single power supply, including reference buffer. Full scale range of the converter is twice of the power supply voltage, i.e. 5.5V. The main design challenges addressed with this design are: 1. the development of very low-power circuit techniques that enable precise sampling of input signal exceeding supply voltage without forward biasing any parasitic body diodes, 2. guaranteeing reliable operation of the devices within this system in which high voltage levels are present, 3. achieving true rail-to-rail signal processing in a single-ended system, 4. achieving 11-bits resolution in a very noisy environment, 5. low power consumption.

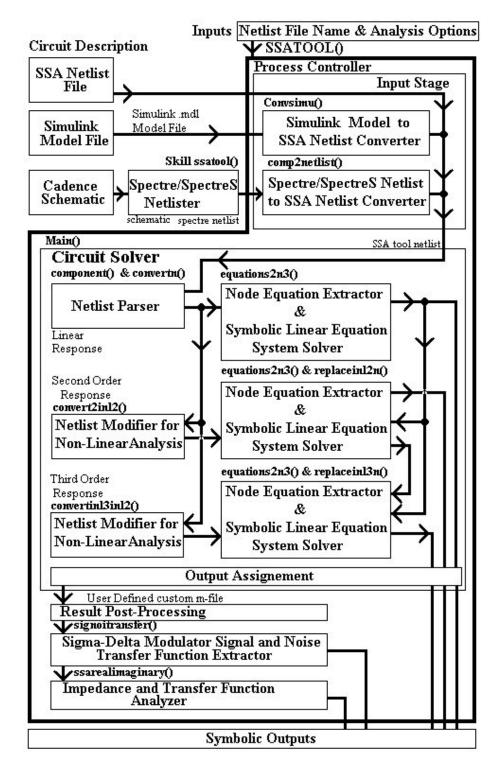

The second topic that this dissertation will address is the development of a symbolic small signal analysis program for linear and non-linear analysis of arbitrary circuits and systems. Symbolic Small Signal Analysis Tool (SSA Tool) is a general purpose tool that calculates small signal response of any given circuit or system symbolically. Matlab and Cadence DFII environments are used as design environment of the tool. The stability analysis of the low drop out voltage regulator designed for the reference signal generation of the analog to digital converter is carried out using SSA Tool. Basically, SSA Tool extracts symbolic node equations from the input that contains the circuit description, and solves the symbolic linear node equation system. The tool is also capable of solving second and third order harmonic and/or inter-modulation distortion responses of any given circuit, provided that the netlist contains required non-linearity calculation related coefficient variables. Using SSA Tool, it is possible to analyze linear and/or non-linear responses of any discrete time systems such as switched capacitor (SC) filters or sigma-delta ( $\Sigma\Delta$ ) modulators. SSA Tool contains several analysis modules to ease sigma-delta modulator analysis, transfer function analysis, impedance/admittance analysis, etc... Developed modules and analysis tool is capable of analyzing symbolically the effects of the linear circuit non-idealities such as finite DC gain of the amplifiers or mismatch error, as well as non-linear large signal errors such as amplifier slew-rate or DAC non-linearity.

# TABLE OF CONTENTS

| PREFA  | ACE    |                                                                                | v   |

|--------|--------|--------------------------------------------------------------------------------|-----|

| ACKN   | OWLI   | EDGMENTS                                                                       | vi  |

| ABSTI  | RACT   |                                                                                | vii |

| Chapte | er 1 I | NTRODUCTION                                                                    | 1   |

| 1.1    | Motiv  | vation and Focus                                                               |     |

|        | or A   | Prayer for the Digital World                                                   | 1   |

| 1.2    | Conte  | ent of the Work                                                                |     |

|        | and I  | Design Challenges                                                              | 4   |

| 1.3    | Contr  | ibutions                                                                       | 8   |

|        | 1.3.1  | High-Voltage Bootstrapped Sampling Switch:                                     |     |

|        |        | New Horizon in ADC System Level Design                                         | 9   |

| 1.4    | Resul  | ts and Achievements                                                            | 12  |

| 1.5    | Orgai  | nization of the Dissertation                                                   | 14  |

| Chapte | er 2 L | ITERATURE REVIEW                                                               | 15  |

| 2.1    | Intro  | luction                                                                        | 15  |

| 2.2    | Power  | r Management ICs (PIC) and Analog to Digital Converters                        | 15  |

|        | 2.2.1  | Market Demand and Requirements                                                 | 15  |

|        | 2.2.2  | PIC system Sub-blocks                                                          | 16  |

|        | 2.2.3  | Analog To Digital Converter Requirements                                       | 17  |

|        | 2.2.4  | Monitoring Input Signals Exceeding the Supply Voltage:                         |     |

|        |        | Solutions, Problems, Trade-offs                                                | 18  |

|        | 2.2.5  | Noise and Isolation strategy and Circuit/System Level Design Issues $\ \ldots$ | 21  |

|        | 2.2.6  | Comparison of the Designed ADC with the Performance of the Available           |     |

|        |        | PIC ADCs.                                                                      | 22  |

| 2.3    | Symb   | olic Circuit Solvers                                                           | 24  |

|        | 2.3.1  | History                                                                        | 24  |

|        | 2.3.2  | Definiton                                                                      | 25  |

|        | 2.3.3  | Applications of Symbolic Analysis: What is it good for ?                       | 25  |

|        | 2.3.4  | Symbolic Analysis Process Flow and Performance                                 | 26  |

| Chapt | er 3 1 | 1-BITS ANALOG TO DIGITAL CONVERTER FOR POWER MAN-                   |    |

|-------|--------|---------------------------------------------------------------------|----|

| AG    | EMEN   | NT ICs                                                              | 30 |

| 3.1   | Intro  | duction                                                             | 30 |

| 3.2   | Archi  | tecture selection for 11 bits Analog to Digital Converter           | 31 |

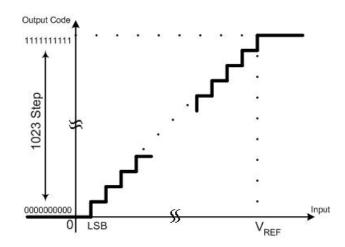

|       | 3.2.1  | Successive-Approximation Register (SAR) Analog to Digital Converter |    |

|       |        | Basics                                                              | 32 |

|       | 3.2.2  | Extending the Input Range of a Regular SAR ADC                      | 33 |

|       | 3.2.3  | 11-bits Sub-Ranging SAR Analog to Digital Converter:                |    |

|       |        | Better Noise Immunity                                               | 36 |

| 3.3   | High-  | Voltage Bootstrapped Sampling Switch (HVB)                          | 39 |

|       | 3.3.1  | Bootstrapped Sampling Switch:                                       |    |

|       |        | Prior Art                                                           | 39 |

|       | 3.3.2  | Techniques to improve reliability                                   | 41 |

|       | 3.3.3  | Limitations of the Traditional switch                               | 41 |

|       | 3.3.4  | Towards supply-voltage independent sampling switch:                 |    |

|       |        | Novel High-Voltage Bootstrapped Sampling Switch                     | 42 |

|       | 3.3.5  | Reliability issues of the Novel Switch                              | 45 |

|       | 3.3.6  | Simulation and Measurement Results                                  | 46 |

| 3.4   | High-  | Voltage Passive Subtractor (HPS)                                    | 49 |

|       | 3.4.1  | Ideal Transfer Function                                             | 49 |

|       | 3.4.2  | Passive Subtractor Transfer Function                                | 51 |

|       | 3.4.3  | DC response and output error due to parasitic capacitance $C_P$     | 53 |

|       | 3.4.4  | Settling Time                                                       | 54 |

|       | 3.4.5  | Filtering                                                           | 55 |

|       | 3.4.6  | The effect of switch channel charge injection                       | 56 |

|       | 3.4.7  | Power issues                                                        | 57 |

|       | 3.4.8  | Design guideline for performance and reliability                    | 57 |

|       | 3.4.9  | Simulation results                                                  | 58 |

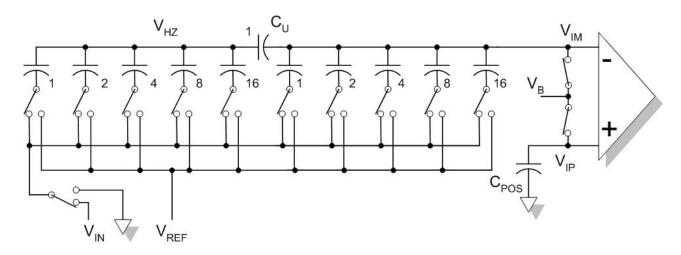

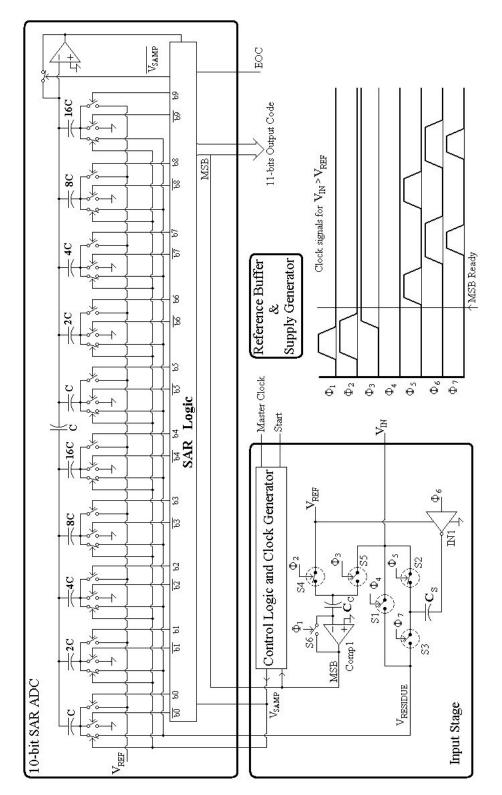

| 3.5   | 10-bit | t Successive-Approximation Register Analog to Digital Converter     | 60 |

|       | 3.5.1  | Coupling Capacitor and the Transfer function                        | 63 |

|       | 3.5.2  | Thermometric Decoding                                               | 65 |

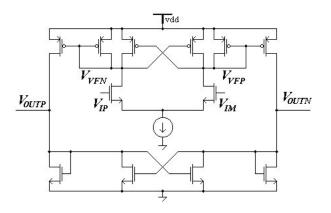

|       | 3.5.3  | Comparator                                                          | 66 |

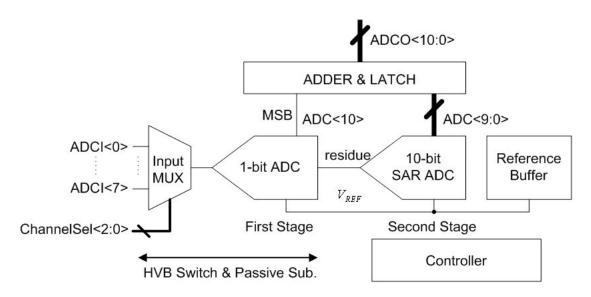

| 3.6   | 11-bit | t Sub-Ranging Analog to Digital Converter                           | 67 |

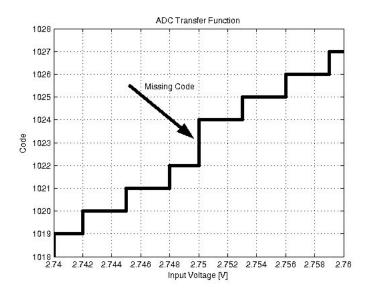

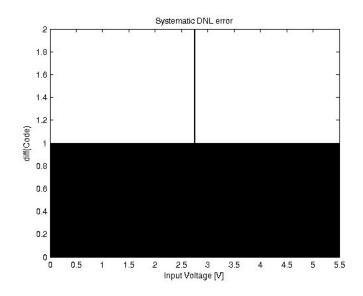

|       | 3.6.1  | Connecting the stages                                               | 67 |

|       | 3.6.2  | Removing the Missing Code                                           | 69 |

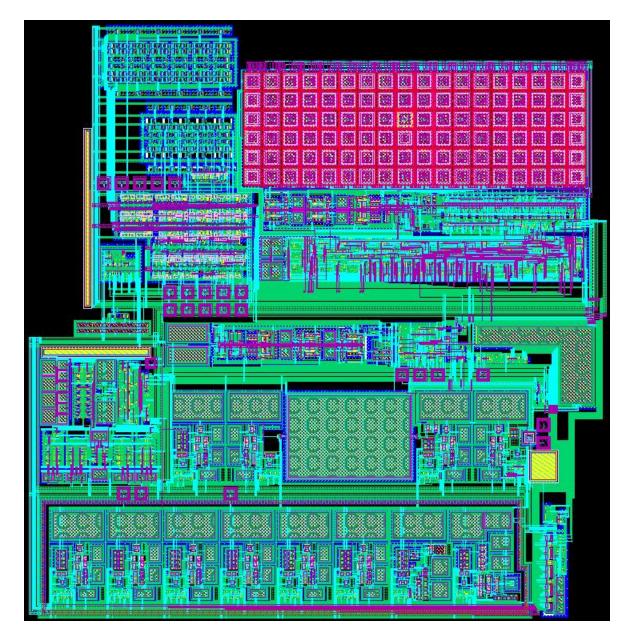

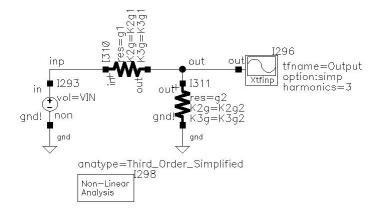

|       | 3.6.3  | 11 bits ADC Layout                                                  | 69 |

|       |        |                                                                     |    |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Chapte | er 4 SYMBOLIC SMALL SIGNAL ANALYZER                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------|-----|

| 4.2       Process Flow, Control And the Outputs       73         4.3       Input Stage and Circuit Description (Input)       77         4.3.1       The basics of the text based SSA Tool netlist file       78         4.3.2       Symbolic Variable Definitions and Restrictions       82         4.3.3       Design Flow using Matlab Simulink schematic capture tool       84         4.3.4       Design Flow using Cadence DFII Virtuoso schematic capture tool       86         4.4       Circuit Solver       89         4.5       Result Post-Processing       91         4.6       Executing the Automation of $\Sigma\Delta$ Modulator Design and Optimization       92         4.6.1       Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization       92         4.6.3       Simplification of the Symbolic Expressions       93         4.6.4       Stability Analysis       94         4.6.5 $\Sigma\Delta$ Analysis Module       95         4.7       Transfer Function Analysis Module       98         4.8       Custom Model Definition       100         4.9       Basics of Non-Linear Analysis       101         4.9.1       Analysis Module       98         4.8       Custom Model Definition       105         4.9.2       Linear respon     | SSA    | A Tool                                                                                      | 72  |

| 4.3       Input Stage and Circuit Description (Input)       77         4.3.1       The basics of the text based SSA Tool netlist file       78         4.3.2       Symbolic Variable Definitions and Restrictions       82         4.3.3       Design Flow using Matlab Simulink schematic capture tool       84         4.3.4       Design Flow using Cadence DFII Virtuoso schematic capture tool       86         4.4       Circuit Solver       89         4.5       Result Post-Processing       91         4.6 $\Sigma \Delta$ Modulator Analysis Module       92         4.6.1       Towards the Automation of $\Sigma \Delta$ Modulator Design and Optimization       92         4.6.2       Executing the $\Sigma \Delta$ Analysis Module       93         4.6.3       Simplification of the Symbolic Expressions       93         4.6.4       Stability Analysis       94         4.6.5 $\Sigma \Delta$ Analysis Module       95         4.7       Transfer Function Analysis Module       98         4.8       Custom Model Definition       100         4.9       Basics of Non-Linear Analysis       101         4.9.1       Analysis Module       98         4.8       Custom Model Definition       100         4.9       Basics of Non-Linear Resistive Divider: Introduc | 4.1    | Introduction                                                                                | 72  |

| 4.3.1 The basics of the text based SSA Tool netlist file784.3.2 Symbolic Variable Definitions and Restrictions824.3.3 Design Flow using Matlab Simulink schematic capture tool844.3.4 Design Flow using Cadence DFII Virtuoso schematic capture tool864.4 Circuit Solver894.5 Result Post-Processing914.6 $\Sigma \Delta$ Modulator Analysis Module924.6.1 Towards the Automation of $\Sigma \Delta$ Modulator Design and Optimization924.6.2 Executing the $\Sigma \Delta$ Analysis Module934.6.3 Simplification of the Symbolic Expressions934.6.4 Stability Analysis944.6.5 $\Sigma \Delta$ Analysis Module function: ssasdmodule() and the Outputs of the module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                           | 4.2    | Process Flow, Control And the Outputs                                                       | 73  |

| 4.3.2Symbolic Variable Definitions and Restrictions\$24.3.3Design Flow using Matlab Simulink schematic capture tool\$44.3.4Design Flow using Cadence DFII Virtuoso schematic capture tool\$64.4Circuit Solver\$94.5Result Post-Processing914.6 $\Sigma \Delta$ Modulator Analysis Module924.6.1Towards the Automation of $\Sigma \Delta$ Modulator Design and Optimization924.6.2Executing the $\Sigma \Delta$ Analysis Module934.6.3Simplification of the Symbolic Expressions934.6.4Stability Analysis944.6.5 $\Sigma \Delta$ Analysis Module954.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test board design1165.3Test Instruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Passive Subtractor1225.4.311 bit Sub-Ranging ADC Performance122Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                         | 4.3    | Input Stage and Circuit Description (Input)                                                 | 77  |

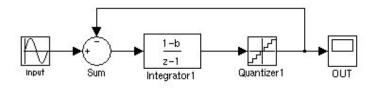

| 4.3.3 Design Flow using Matlab Simulink schematic capture tool844.3.4 Design Flow using Cadence DFII Virtuoso schematic capture tool864.4 Circuit Solver894.5 Result Post-Processing914.6 $\Sigma \Delta$ Modulator Analysis Module924.6.1 Towards the Automation of $\Sigma \Delta$ Modulator Design and Optimization924.6.2 Executing the $\Sigma \Delta$ Analysis Module934.6.3 Simplification of the Symbolic Expressions934.6.4 Stability Analysis944.6.5 $\Sigma \Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                        |        | 4.3.1 The basics of the text based SSA Tool netlist file                                    | 78  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 4.3.2 Symbolic Variable Definitions and Restrictions                                        | 82  |

| 4.4Circuit Solver894.5Result Post-Processing914.6 $\Sigma\Delta$ Modulator Analysis Module924.6.1Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization924.6.2Executing the $\Sigma\Delta$ Analysis Module934.6.3Simplification of the Symbolic Expressions934.6.4Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test lastruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Bootstrapped Switch1205.4.2High-Voltage Passive Subtractor1225.4.311bit Sub-Ranging ADC Performance122Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                 |        | 4.3.3 Design Flow using Matlab Simulink schematic capture tool                              | 84  |

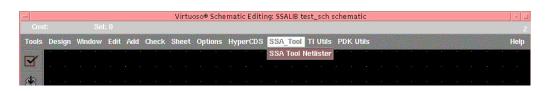

| 4.5Result Post-Processing914.6 $\Sigma\Delta$ Modulator Analysis Module924.6.1Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization924.6.2Executing the $\Sigma\Delta$ Analysis Module934.6.3Simplification of the Symbolic Expressions934.6.4Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: sasdmodule() and the Outputs of the<br>module954.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test Instruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Bootstrapped Switch1205.4.311bit Sub-Ranging ADC Performance122Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                            |        | 4.3.4 Design Flow using Cadence DFII Virtuoso schematic capture tool                        | 86  |

| 4.6 $\Sigma\Delta$ Modulator Analysis Module .924.6.1Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization924.6.2Executing the $\Sigma\Delta$ Analysis Module934.6.3Simplification of the Symbolic Expressions934.6.4Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: sasdmodule() and the Outputs of the<br>module954.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test Instruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Bootstrapped Switch1205.4.311bit Sub-Ranging ADC Performance122Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                     | 4.4    | Circuit Solver                                                                              | 89  |

| 4.6.1 Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization924.6.2 Executing the $\Sigma\Delta$ Analysis Module934.6.3 Simplification of the Symbolic Expressions934.6.4 Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                            | 4.5    | Result Post-Processing                                                                      | 91  |

| 4.6.2 Executing the $\Sigma\Delta$ Analysis Module934.6.3 Simplification of the Symbolic Expressions934.6.4 Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.6    | $\Sigma\Delta$ Modulator Analysis Module                                                    | 92  |

| 4.6.3 Simplification of the Symbolic Expressions934.6.4 Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 4.6.1 Towards the Automation of $\Sigma\Delta$ Modulator Design and Optimization $\hdots$ . | 92  |

| 4.6.4 Stability Analysis944.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 4.6.2 Executing the $\Sigma\Delta$ Analysis Module $\ldots$                                 | 93  |

| 4.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the<br>module954.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test loard design1165.3Test Instruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Bootstrapped Switch1205.4.2High-Voltage Passive Subtractor1225.4.311bit Sub-Ranging ADC Performance126Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 4.6.3 Simplification of the Symbolic Expressions                                            | 93  |

| module954.7 Transfer Function Analysis Module984.8 Custom Model Definition1004.9 Basics of Non-Linear Analysis1014.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 4.6.4 Stability Analysis                                                                    | 94  |

| 4.7Transfer Function Analysis Module984.8Custom Model Definition1004.9Basics of Non-Linear Analysis1014.9.1Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2Linear responses1064.9.3Second order harmonic responses1064.9.4Third order harmonic responses108Chapter 5EXPERIMENTAL RESULTS1125.1Technology Overview and the Test Die1125.2Test board design1165.3Test Instruments, Setup and Procedure1175.4Measurement Results1195.4.1High-Voltage Bootstrapped Switch1205.4.2High-Voltage Passive Subtractor1225.4.311 bit Sub-Ranging ADC Performance126Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        | 4.6.5 $\Sigma\Delta$ Analysis Module function: ssasdmodule() and the Outputs of the         |     |

| 4.8       Custom Model Definition       100         4.9       Basics of Non-Linear Analysis       101         4.9.1       Analysis of a Non-Linear Resistive Divider: Introduction       105         4.9.2       Linear responses       106         4.9.3       Second order harmonic responses       106         4.9.4       Third order harmonic responses       106         4.9.4       Third order harmonic responses       108         Chapter 5       EXPERIMENTAL RESULTS       112         5.1       Technology Overview and the Test Die       112         5.2       Test board design       116         5.3       Test Instruments, Setup and Procedure       117         5.4       Measurement Results       119         5.4.1       High-Voltage Bootstrapped Switch       120         5.4.2       High-Voltage Passive Subtractor       122         5.4.3       11 bit Sub-Ranging ADC Performance       122         Chapter 6       SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                           |        | module                                                                                      | 95  |

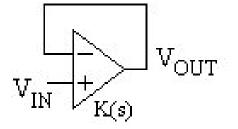

| 4.9 Basics of Non-Linear Analysis       101         4.9.1 Analysis of a Non-Linear Resistive Divider: Introduction       105         4.9.2 Linear responses       106         4.9.3 Second order harmonic responses       106         4.9.4 Third order harmonic responses       108         Chapter 5 EXPERIMENTAL RESULTS       112         5.1 Technology Overview and the Test Die       112         5.2 Test board design       116         5.3 Test Instruments, Setup and Procedure       117         5.4 Measurement Results       119         5.4.1 High-Voltage Bootstrapped Switch       120         5.4.2 High-Voltage Passive Subtractor       122         5.4.3 11 bit Sub-Ranging ADC Performance       122         Chapter 6 SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.7    | Transfer Function Analysis Module                                                           | 98  |

| 4.9.1 Analysis of a Non-Linear Resistive Divider: Introduction1054.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.8    | Custom Model Definition                                                                     | 100 |

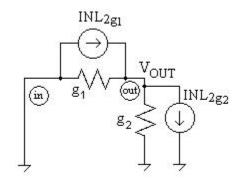

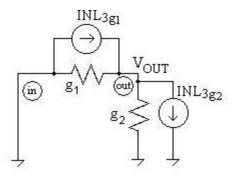

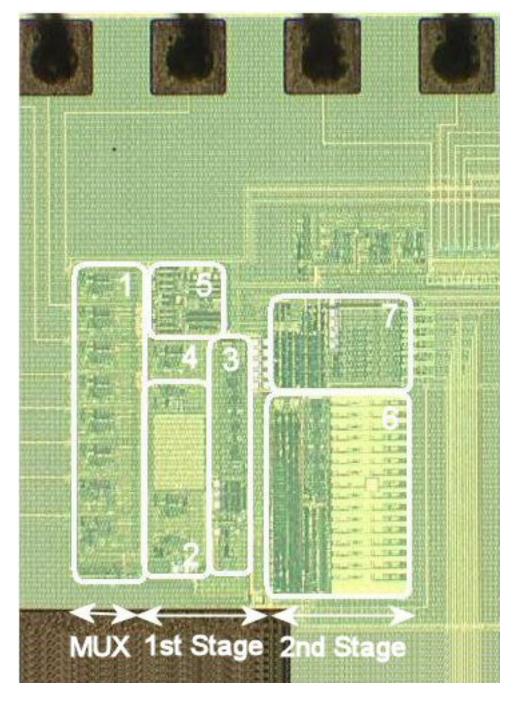

| 4.9.2 Linear responses1064.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.9    | Basics of Non-Linear Analysis                                                               | 101 |

| 4.9.3 Second order harmonic responses1064.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance126Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 4.9.1 Analysis of a Non-Linear Resistive Divider: Introduction                              | 105 |

| 4.9.4 Third order harmonic responses108Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 4.9.2 Linear responses                                                                      | 106 |

| Chapter 5 EXPERIMENTAL RESULTS1125.1 Technology Overview and the Test Die1125.2 Test board design1165.3 Test Instruments, Setup and Procedure1175.4 Measurement Results1195.4.1 High-Voltage Bootstrapped Switch1205.4.2 High-Voltage Passive Subtractor1225.4.3 11 bit Sub-Ranging ADC Performance122Chapter 6 SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 4.9.3 Second order harmonic responses                                                       | 106 |

| 5.1       Technology Overview and the Test Die       112         5.2       Test board design       116         5.3       Test Instruments, Setup and Procedure       117         5.4       Measurement Results       119         5.4.1       High-Voltage Bootstrapped Switch       120         5.4.2       High-Voltage Passive Subtractor       122         5.4.3       11 bit Sub-Ranging ADC Performance       122         Chapter 6       SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | 4.9.4 Third order harmonic responses                                                        | 108 |

| 5.2       Test board design       116         5.3       Test Instruments, Setup and Procedure       117         5.4       Measurement Results       119         5.4.1       High-Voltage Bootstrapped Switch       120         5.4.2       High-Voltage Passive Subtractor       122         5.4.3       11       bit Sub-Ranging ADC Performance       122         Chapter 6       SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Chapte | er 5 EXPERIMENTAL RESULTS                                                                   | 112 |

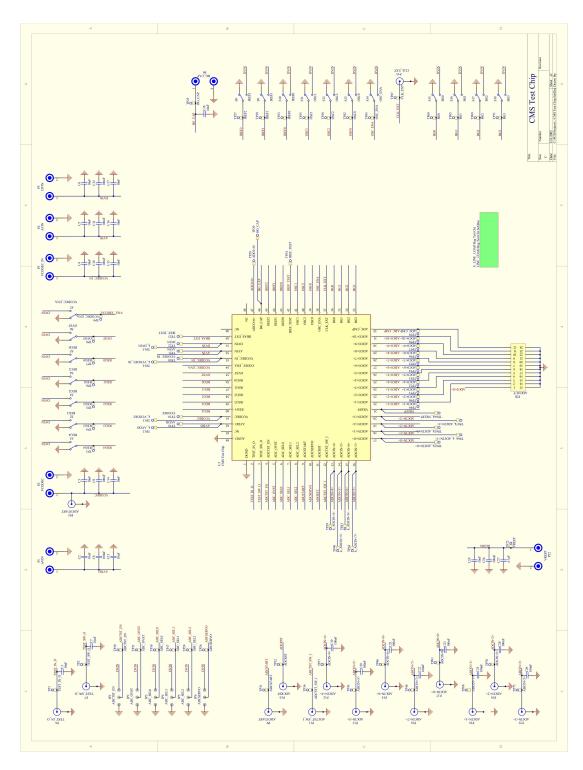

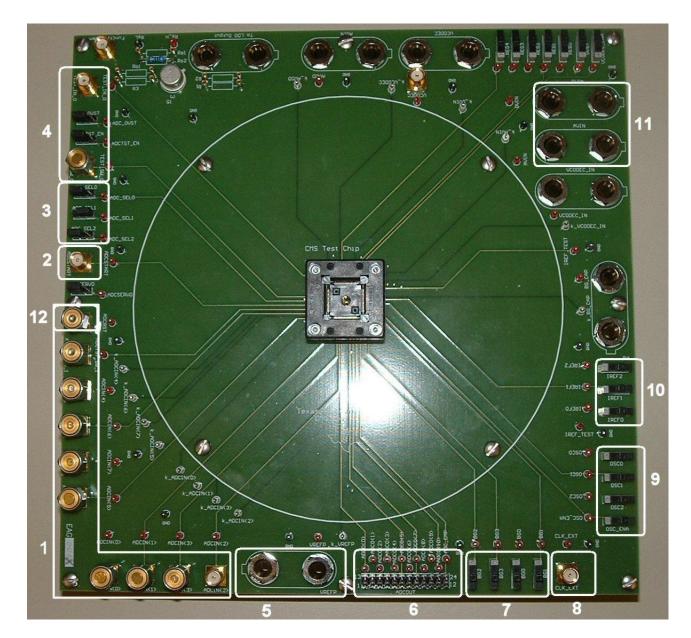

| 5.3 Test Instruments, Setup and Procedure       117         5.4 Measurement Results       119         5.4.1 High-Voltage Bootstrapped Switch       120         5.4.2 High-Voltage Passive Subtractor       122         5.4.3 11 bit Sub-Ranging ADC Performance       122         Chapter 6 SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.1    | Technology Overview and the Test Die                                                        | 112 |

| 5.4 Measurement Results       119         5.4.1 High-Voltage Bootstrapped Switch       120         5.4.2 High-Voltage Passive Subtractor       122         5.4.3 11 bit Sub-Ranging ADC Performance       122         Chapter 6 SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2    | Test board design                                                                           | 116 |

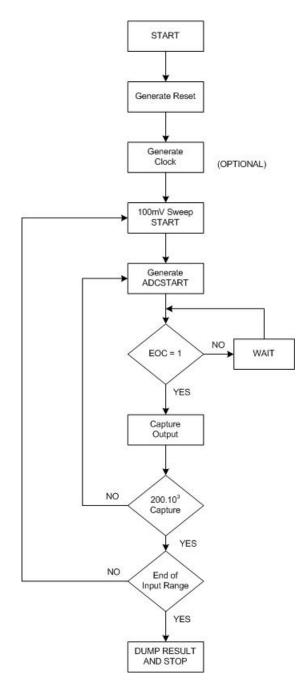

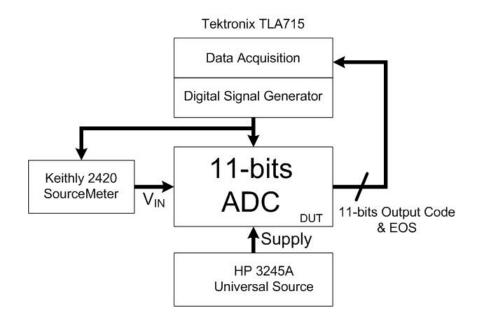

| 5.4.1 High-Voltage Bootstrapped Switch       120         5.4.2 High-Voltage Passive Subtractor       122         5.4.3 11 bit Sub-Ranging ADC Performance       122         Chapter 6 SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.3    | Test Instruments, Setup and Procedure                                                       | 117 |

| 5.4.2 High-Voltage Passive Subtractor       122         5.4.3 11 bit Sub-Ranging ADC Performance       122         Chapter 6 SOFTWARE VALIDATION       126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4    | Measurement Results                                                                         | 119 |

| 5.4.311 bit Sub-Ranging ADC Performance122Chapter 6SOFTWARE VALIDATION126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | 5.4.1 High-Voltage Bootstrapped Switch                                                      | 120 |

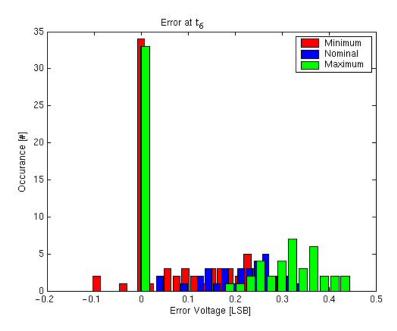

| Chapter 6 SOFTWARE VALIDATION 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 5.4.2 High-Voltage Passive Subtractor                                                       | 122 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 5.4.3 11 bit Sub-Ranging ADC Performance                                                    | 122 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Chapte | er 6 SOFTWARE VALIDATION                                                                    | 126 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      |                                                                                             |     |

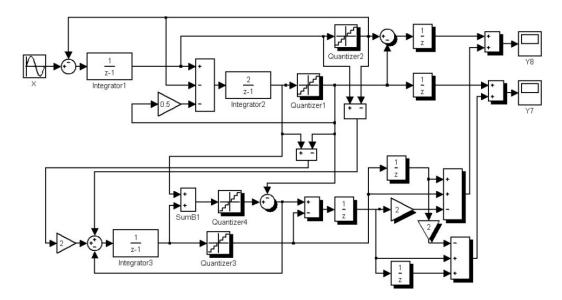

| 6.2    | Exam    | nple : Analysis of the 2-1 MASH Time Interleaved $\Sigma\Delta$ Modulator $\ldots$    | 126 |

|--------|---------|---------------------------------------------------------------------------------------|-----|

|        | 6.2.1   | Output Signal and In Band Noise Power                                                 | 128 |

|        | 6.2.2   | Voltage Swing of the Internal Nodes                                                   | 128 |

|        | 6.2.3   | Noise analysis of the system                                                          | 129 |

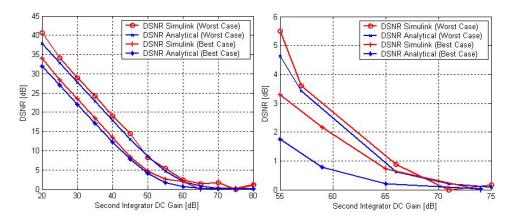

|        | 6.2.4   | The effect of the finite amplifier gain                                               | 129 |

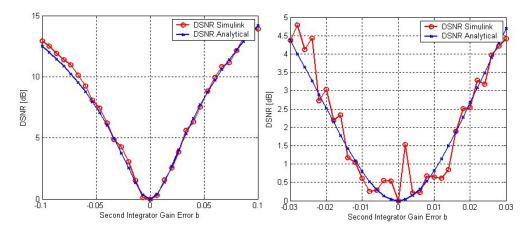

|        | 6.2.5   | The effect of the Integrator Gain Error, Amplifier Linear Settling error              |     |

|        |         | and Non-Zero On-Resistance of the MOS Switches:                                       | 131 |

|        | 6.2.6   | The effect of the Imbalance among the Input Branches                                  | 132 |

| 6.3    | Exam    | aple :                                                                                |     |

|        | Stabi   | lity and Sensitivity Analysis of a $4^{th}$ order Single Bit $\Sigma\Delta$ Modulator | 133 |

|        | 6.3.1   | The Modulator Output Signal                                                           | 136 |

|        | 6.3.2   | Stability analysis                                                                    | 136 |

|        | 6.3.3   | Sensitivity analysis                                                                  | 137 |

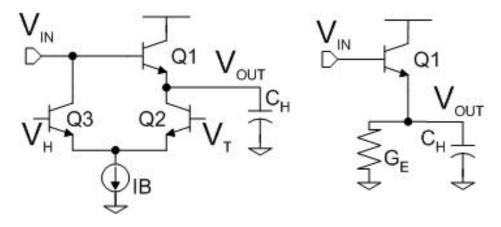

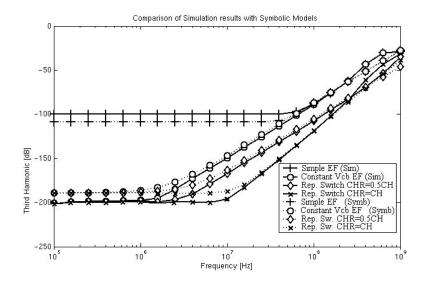

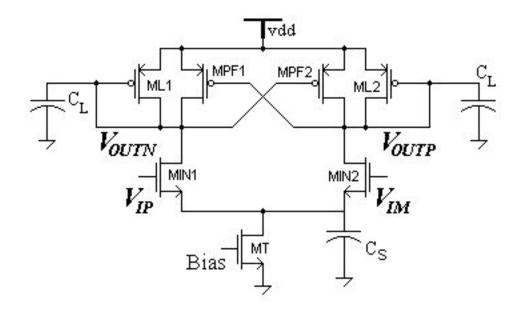

| 6.4    | Exam    | pple : Non-Linear Analysis Of Switched Emitter Follower:                              |     |

|        | How     | to improve its linearity.                                                             | 138 |

|        | 6.4.1   | Problem Definition                                                                    | 138 |

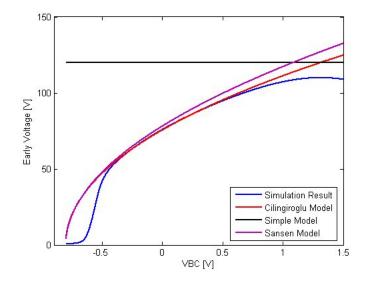

|        | 6.4.2   | Nonlinear Bipolar Junction Transistor Device Model Selection                          | 139 |

|        | 6.4.3   | Nonlinear Analysis of Emitter Follower                                                | 141 |

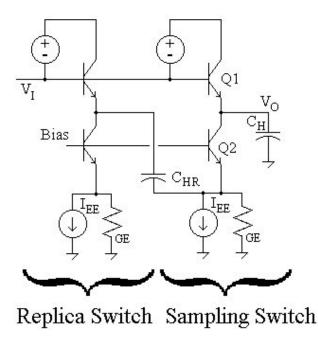

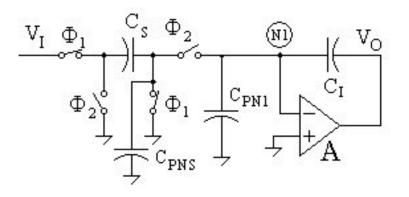

|        | 6.4.4   | Improving Low frequency Distortion Performance                                        | 142 |

|        | 6.4.5   | Improving High frequency Distortion Performance                                       | 143 |

|        | 6.4.6   | Comparison of the Analytical Results with the Simulation Results                      | 145 |

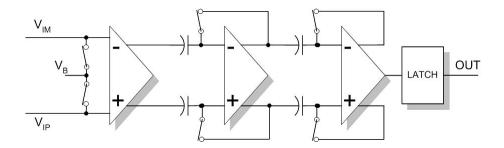

| 6.5    | Exam    | nple : Small Signal Analysis of ADC Comparator Input stage                            | 145 |

| Chapte | er7 (   | CONCLUSION                                                                            | 149 |

| Annen  | div A   | The Effect of the finite Amplifier Gain to the performance of an SC                   |     |

|        | grator  |                                                                                       | 150 |

| Inte   | ,510001 |                                                                                       | 100 |

| Appen  | dix B   | Signal to Noise Ratio Degradation Due to Excess In Band Noise:                        |     |

| Defi   | inition | of $\Delta$ SNR                                                                       | 152 |

| Appen  | dix C   | The Effect of the Linear Settling Error of the Amplifier                              | 154 |

| Appen  | dix D   | The Effect of the Switch On-Resistance                                                | 155 |

| Appen  | dix E   | High Voltage Bootstrapped Sampling Switches: Evolution                                | 157 |

| E.1    | First   | Version of The Sampling Switch                                                        | 157 |

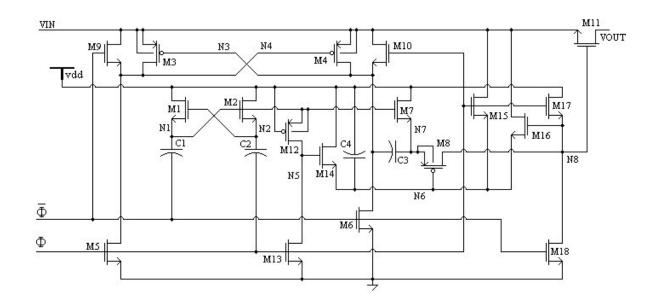

| E.2    | Impro   | oved Version of the Sampling Switch                                                   | 160 |

| E.3    | Comp    | parison of All three Sampling Switch                                                  | 163 |

|        |         |                                                                                       |     |

| E.4 Extending the Range of the Level Shifter Or Thin Oxide Implementation $\ldots$ | 163 |

|------------------------------------------------------------------------------------|-----|

| E.5 Reliability issues, Switch performance degradation, Device/Circuit life-time   | 165 |

| Appendix F SSA Tool Known Problem and Issues                                       | 169 |

| Appendix G Non-Linearity Coefficients of a Bipolar Transistor                      | 171 |

| Appendix H SSA Tool Library                                                        | 173 |

| BIBLIOGRAPHY                                                                       | 174 |

| VITA                                                                               |     |

# LIST OF FIGURES

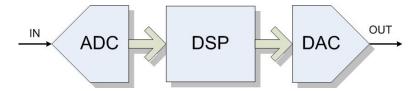

| 1.1  | Typical signal processing path                                                                 | 2  |

|------|------------------------------------------------------------------------------------------------|----|

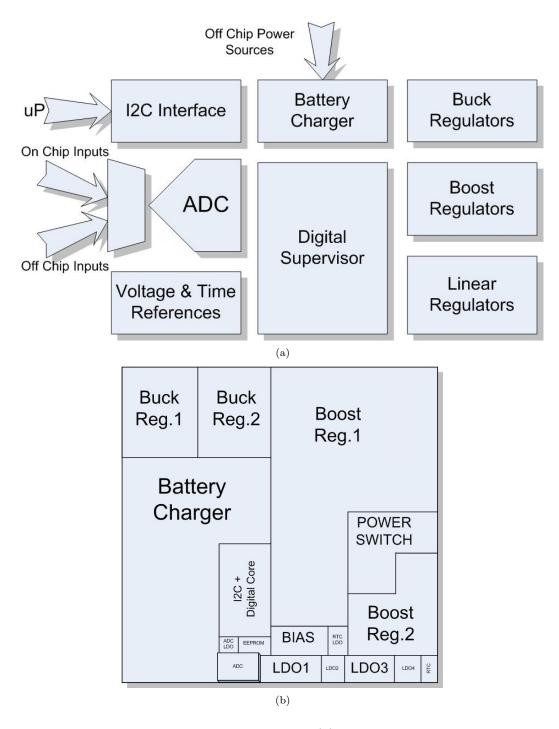

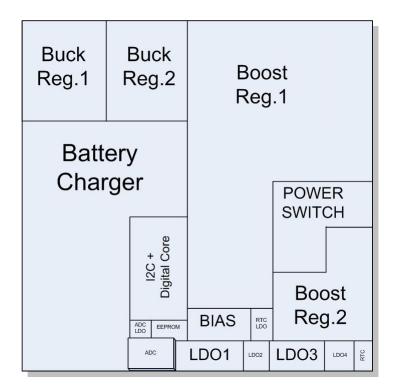

| 1.2  | A modern Power Management IC, (a) Typical System Block Diagram, (b)                            |    |

|      | Typical Floorplan                                                                              | 5  |

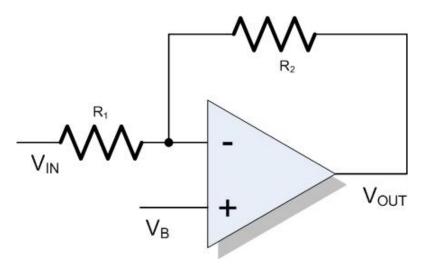

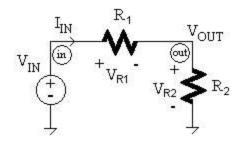

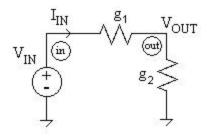

| 2.1  | Input Rescaling Using Feedback Amplifier for Low Output Impedance                              | 19 |

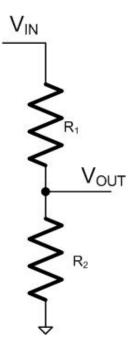

| 2.2  | Input Rescaling Using Resistive Divider, High Output Impedance                                 | 20 |

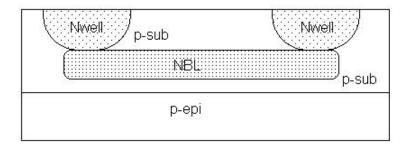

| 2.3  | NBL - NWell Tank Isolation                                                                     | 22 |

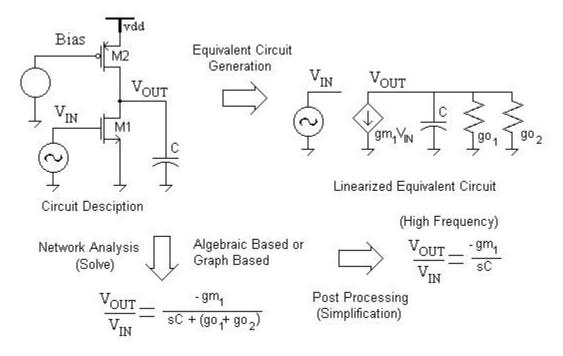

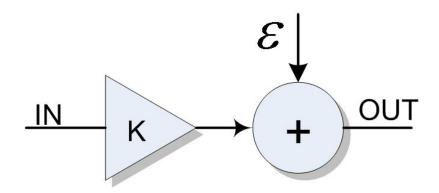

| 2.4  | Basic Process Flow of Symbolic Circuit Analyzer From Circuit Description to                    |    |

|      | Symbolic Transfer Function                                                                     | 26 |

| 3.1  | A modern Power Management IC's Typical Floorplan                                               | 32 |

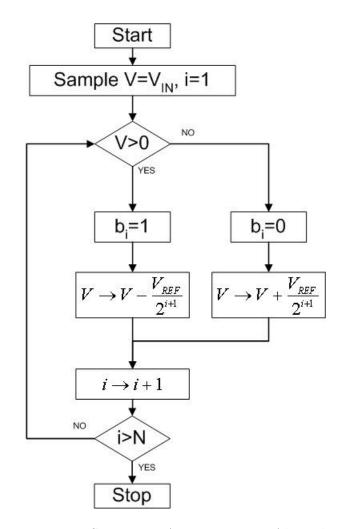

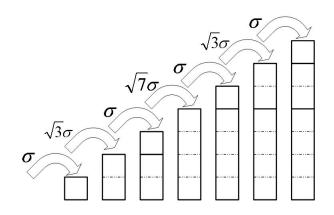

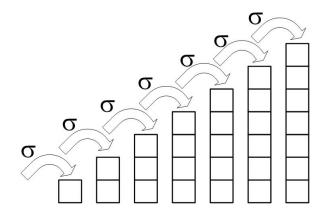

| 3.2  | Successive-Approximation Algorithm                                                             | 34 |

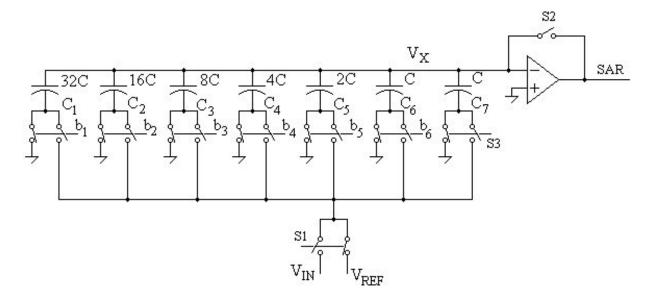

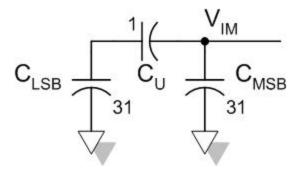

| 3.3  | Charge-Redistribution SAR Converter core                                                       | 35 |

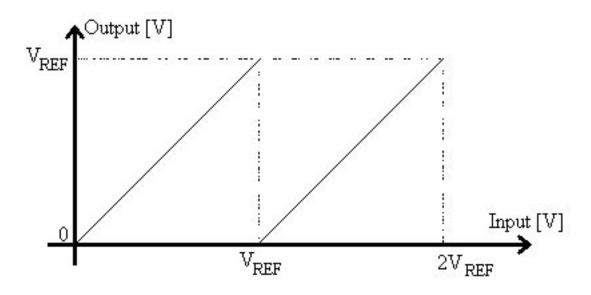

| 3.4  | Extending the Input Signal Range of a Regular SAR ADC                                          | 36 |

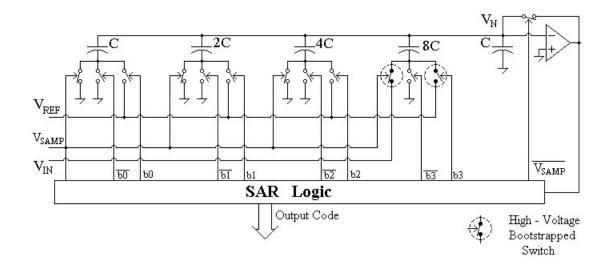

| 3.5  | 11 bits Sub-Ranging SAR Analog to Digital Converter                                            | 37 |

| 3.6  | Classical Bootstrapped Switch                                                                  | 40 |

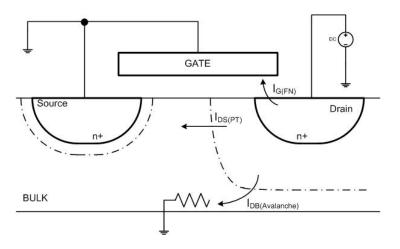

| 3.7  | The current path due to the parasitic body diode of $M_4$                                      | 42 |

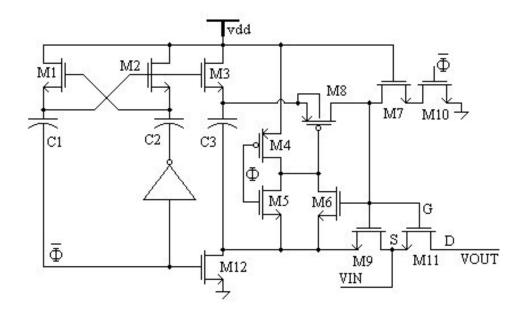

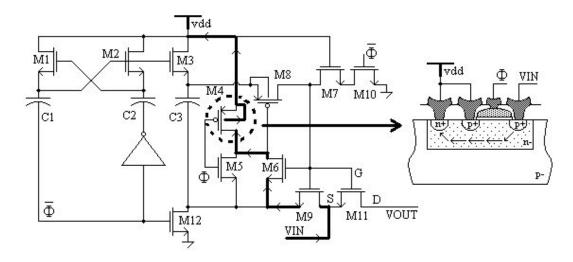

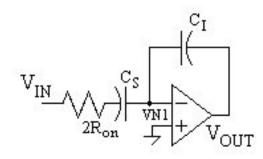

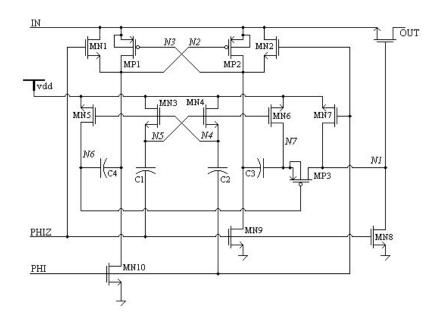

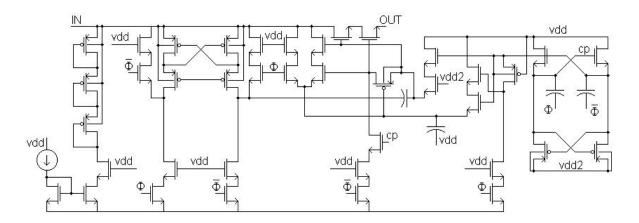

| 3.8  | Proposed High-Voltage Bootstrapped Sampling Switch                                             | 43 |

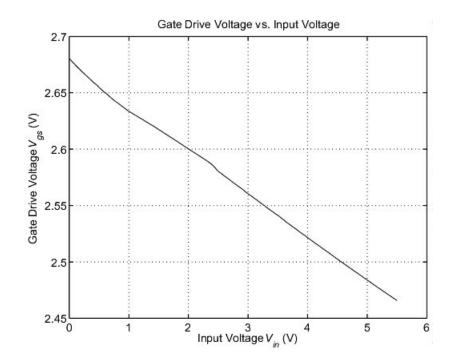

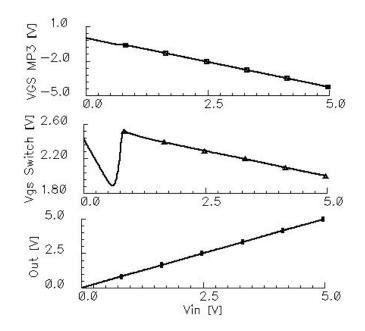

| 3.9  | Gate Drive Voltage $V_{GS}$ vs. Input Voltage $V_{IN}$                                         | 47 |

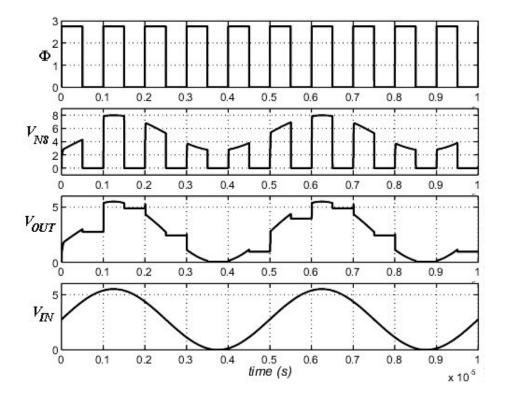

| 3.10 | Simulated Switch Behavior with a Dynamically Changing Input Signal                             | 47 |

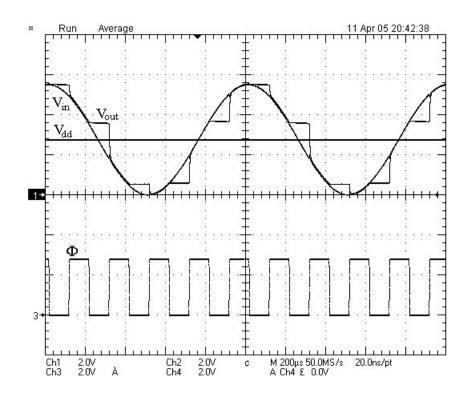

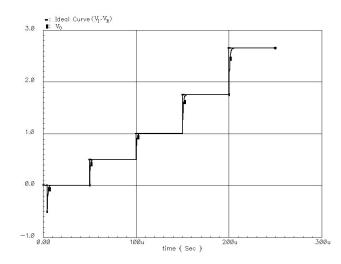

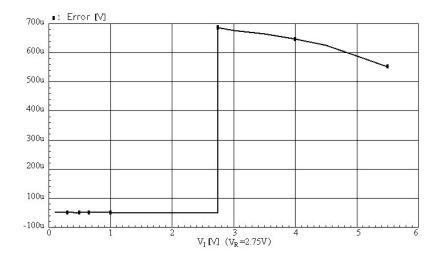

| 3.11 | Measured Switch Behavior with a dynamically Changing Input Signal                              | 50 |

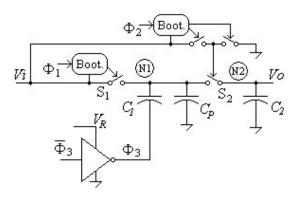

| 3.12 | Simplified Schematic of HPS                                                                    | 51 |

| 3.13 | Simplified Schematic of HPS                                                                    | 52 |

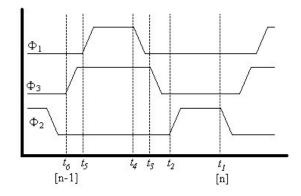

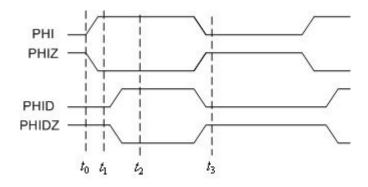

| 3.14 | Switching timing diagram of HPS                                                                | 52 |

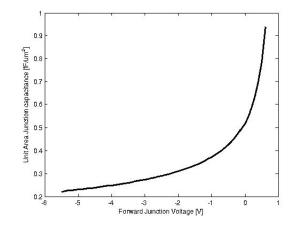

| 3.15 | 5 Unit Area capacitance variation of a junction capacitance for typical CMOS                   |    |

|      | process                                                                                        | 54 |

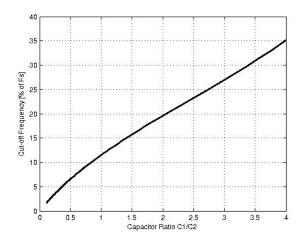

| 3.16 | 5-3dB Bandwidth of the passive subtractor as a percentage of sampling frequency                |    |

|      | $F_S$ for different $C_1/C_2$ ratio                                                            | 56 |

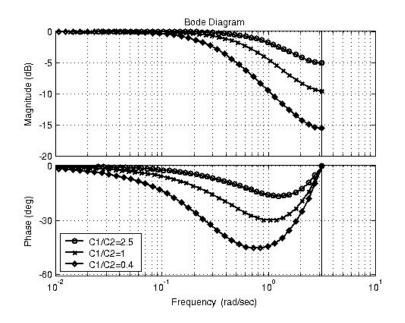

| 3.17 | 7 The Bode plot of the passive subtractor for different $C_1/C_2$ ratio $\ldots \ldots \ldots$ | 57 |

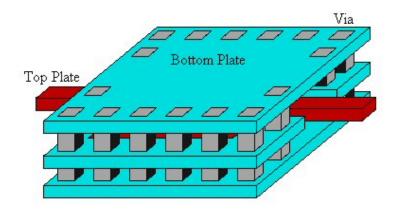

| 3.18 | Suggested Layout for the Capacitor $C_1$                                                       | 58 |

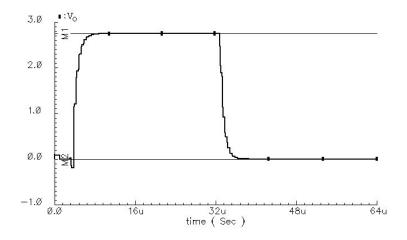

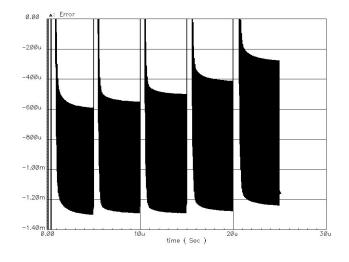

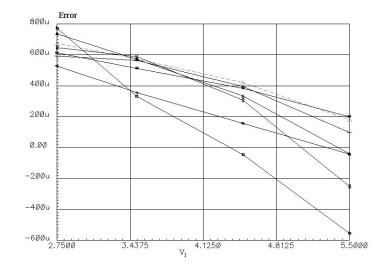

| 3.19 | Transient Simulation of HPS (Input signal changes from 5.5V to 2.751V at $32\mu$ s)            | 59 |

| 5.3  | PCB Board Photo                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 5.4  | Test Procedure                                                                                                        |

| 5.5  | Test Setup                                                                                                            |

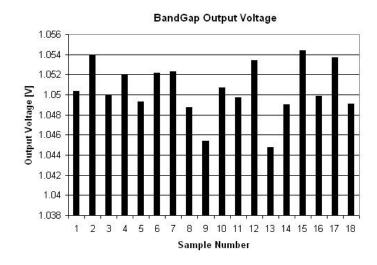

| 5.6  | Measured Untrimmed BandGap Voltages with respect to sample number 120                                                 |

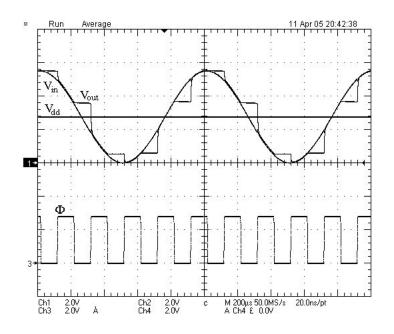

| 5.7  | Measurement result of the High-Voltage Bootstrapped Switch for maximum                                                |

|      | $V_{IN} = 5.5V$ and $V_{dd} = 2.75V$                                                                                  |

| 5.8  | Measurement result of the High-Voltage Bootstrapped Switch for maximum                                                |

|      | $V_{IN} = 6V$ and $V_{dd} = 1.2V$                                                                                     |

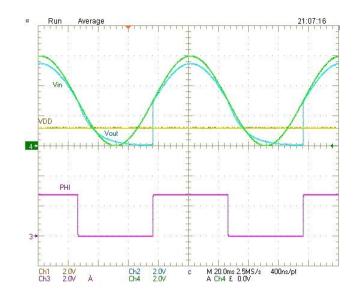

| 5.9  | Measurement result of the High-Voltage Bootstrapped Switch for maximum                                                |

|      | $V_{IN} = 5.5V$ and $V_{dd} = 2.75V$                                                                                  |

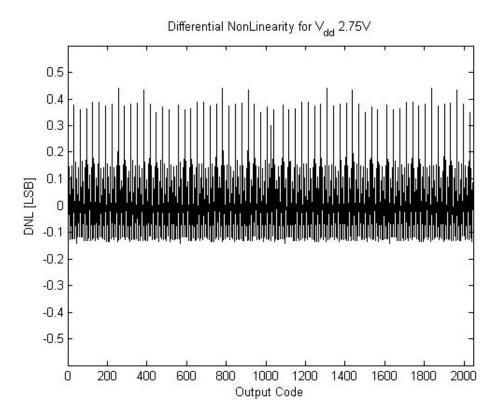

| 5.10 | Differential Nonlinearity of the 11 bit Sub-Ranging ADC                                                               |

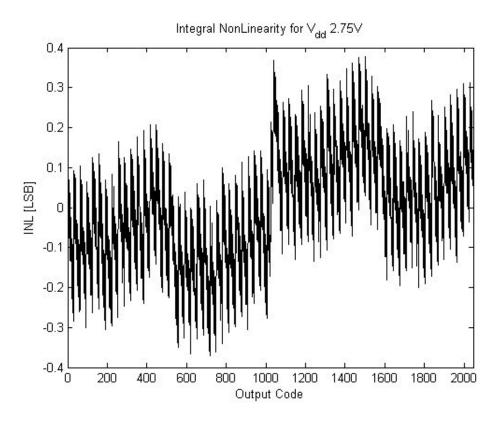

| 5.11 | Integral Nonlinearity of the 11 bit Sub-Ranging ADC                                                                   |

| 6.1  | 2-1 Mash Time Interleaved $\Sigma\Delta$ Modulator Schematic                                                          |

| 6.2  | Comparison of the Simulank Simulation Results with the Analytical Expression                                          |

|      | modeling the effect of the second Integrator's Amplifier Finite DC Gain $\ \ldots \ .$ 131                            |

| 6.3  | Comparison of the Simulank Simulation Results with the Analytical Expression                                          |

|      | modeling the effect of the second Integrator's Gain Error 132                                                         |

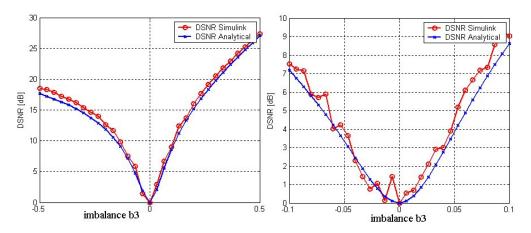

| 6.4  | Comparison of the Simulink Simulation Results with the Analytical Expression                                          |

|      | modeling the SNR degradation due to the imbalance introduced by $b_3$ 133                                             |

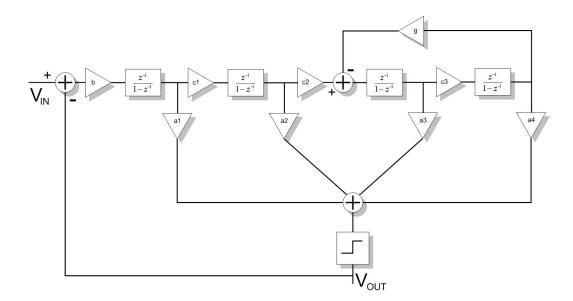

| 6.5  | $4^{th}$ Order Single Bit $\Sigma\Delta$ Modulator Schematic                                                          |

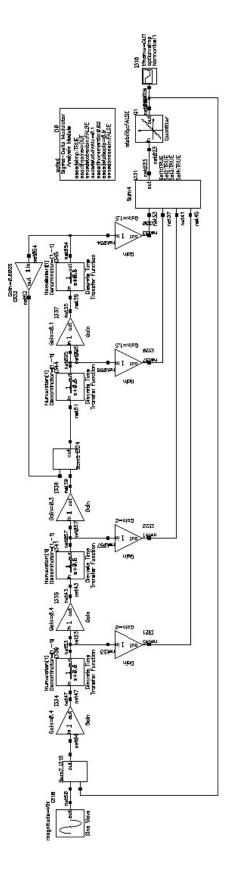

| 6.6  | $4^{th}$ Order Single Bit $\Sigma\Delta$ Modulator Cadence Schematic $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 135 |

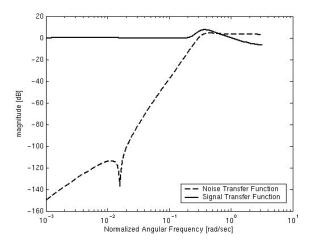

| 6.7  | Signal and Noise Transfer Function of the $\Sigma\Delta$ Modulator                                                    |

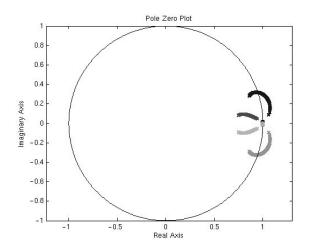

| 6.8  | Root Locus Plot of the $\Sigma\Delta$ Modulator for varying Quantizer Gain                                            |

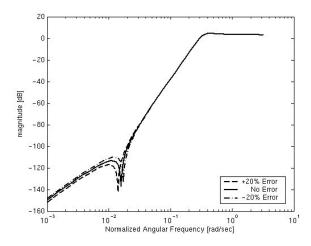

| 6.9  | Sensitivity of the Noise Transfer Function to the parameter $g$                                                       |

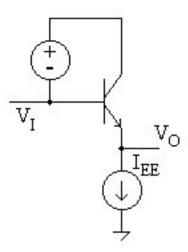

| 6.10 | )<br>Switched Emitter Follower and its equivalent circuit during the tracking mode . $139$                            |

| 6.11 | Variation of the Early Voltage Expressions with respect to the Base-Collector                                         |

|      | Voltage                                                                                                               |

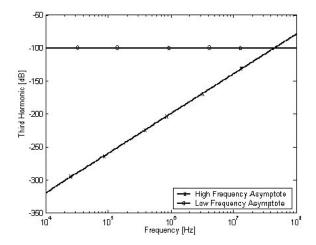

| 6.12 | 2  Low and High Frequency asymptotes of simple Emitter Follower's third harmonic. 142                                 |

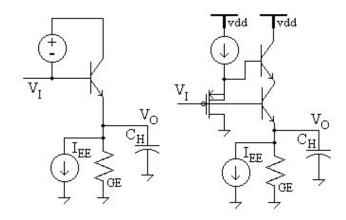

| 6.13 | The basic idea and its circuit implementation to improve low frequency distor-                                        |

|      | tion performance                                                                                                      |

| 6.14 | The basic idea to improve high frequency distortion performance                                                       |

| 6.15 | 5 Replica Switch Implementation to improve high frequency distortion performance 145                                  |

| 6.16 | Comparison of the Simulation and symbolic results                                                                     |

| 6.17 | Input Stage of the Comparator 146                                                                                     |

| 6.18 | New transfer function as result of Input differential pair mismatch                                                   |

| A.1 | Non-Ideal Discrete-Time Integrator                                        | 150 |

|-----|---------------------------------------------------------------------------|-----|

| C.1 | Equivalent Circuit of an SC Block During Settling                         | 154 |

| D.1 | The model for the effect of switch on resistance                          | 155 |

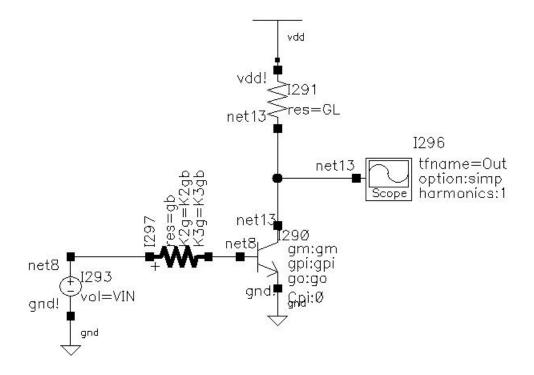

|     | First Version of High-Voltage Bootstrapped Sampling Switch                | 158 |

| E.2 | Simulation Results Of First Version of High-Voltage Bootstrapped Sampling |     |

|     | Switch                                                                    | 160 |

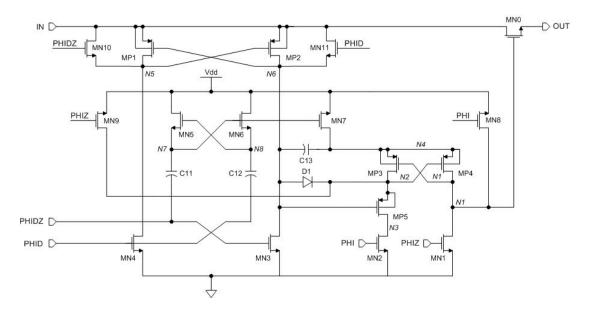

| E.3 | Improved Version of High-Voltage Bootstrapped Sampling Switch             | 161 |

| E.4 | Clock Timing Diagram of Second Sampling Switch                            | 161 |

| E.5 | 3.3V Core CMOS transistor implementation of the High Voltage Bootstrapped |     |

|     | Switch                                                                    | 164 |

| E.6 | Experiment for NMOS device reliability 1                                  | 165 |

# LIST OF TABLES

| 1.1 | Specifications of the 11-bit Sub-Ranging ADC                                                                                                                                                                                                                                                                                    | 13  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Performance parameter list of available PICs in the market together with pre-<br>sented ADC.                                                                                                                                                                                                                                    | 23  |

|     |                                                                                                                                                                                                                                                                                                                                 |     |

| 3.1 | 11-bits ADC Design Specifications                                                                                                                                                                                                                                                                                               | 31  |

| 3.2 | Node voltages during two phases of operation and maximum voltage swing                                                                                                                                                                                                                                                          | 46  |

| 3.3 | Terminal Voltages of the Transistors and the worst case over voltage stress                                                                                                                                                                                                                                                     |     |