# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

# DESIGN AND TESTING OF A HIGHLY-ADAPTABLE RISC-V VERIFICATION ENVIRONMENT

# **SENIOR DESIGN PROJECT**

Mete Kaan ÖZDEN Deniz Zakir EROĞLU

ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

# DESIGN AND TESTING OF A HIGHLY-ADAPTABLE RISC-V VERIFICATION ENVIRONMENT

# **SENIOR DESIGN PROJECT**

Mete Kaan ÖZDEN 040200215

Deniz Zakir EROĞLU 040200249

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

Project Advisor: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> <u>ELEKTRİK-ELEKTRONİK FAKÜLTESİ</u>

# YÜKSEK DERECEDE UYARLANABİLİR BİR RISC-V DOĞRULAMA ORTAMININ TASARIMI VE TEST EDİLMESİ

# LİSANS BİTİRME TASARIM PROJESİ

Mete Kaan ÖZDEN 040200215

Deniz Zakir EROĞLU 040200249

Proje Danışmanı: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

ELEKTRONİK VE HABERLEŞME MÜHENDİSLİĞİ BÖLÜMÜ HAZİRAN, 2025

We are submitting the Senior Design Project Report entitled as "DESIGN AND TESTING OF A HIGHLY-ADAPTABLE RISC-V VERIFICATION ENVIRONMENT". The Senior Design Project Report has been prepared as to fulfill the relevant regulations of the Electronics and Communication Engineering Department of Istanbul Technical University. We hereby confirm that we have realized all stages of the Senior Design Project work by ourselves and we have abided by the ethical rules with respect to academic and professional integrity .

| Mete Kaan ÖZDEN    |  |

|--------------------|--|

| 040200215          |  |

|                    |  |

|                    |  |

| Deniz Zakir EROĞLU |  |

| 040200249          |  |

# **FOREWORD**

We would like to express our gratitude to our advisor Prof. Dr. Sıddıka Berna Örs Yalçın, who dedicated her time for us and provided all the help she could. We also acknowledge the support our families gave us; without which we would not succeed

June 2025

Mete Kaan ÖZDEN Deniz Zakir EROĞLU

# TABLE OF CONTENTS

| $\underline{\mathbf{P}}$                                          | age |

|-------------------------------------------------------------------|-----|

| FOREWORD                                                          | v   |

| TABLE OF CONTENTS                                                 | vii |

| ABBREVIATIONS                                                     |     |

| LIST OF TABLES                                                    |     |

| LIST OF FIGURES                                                   |     |

| SUMMARY                                                           |     |

| ÖZET                                                              |     |

| 1. INTRODUCTION                                                   | 1   |

| 1.1 Purpose of the Project                                        | 1   |

| 1.2 Literature Review                                             | 1   |

| 2. BACKGROUND INFORMATION                                         | 3   |

| 2.1 About RISC-V and Hornet                                       | 3   |

| 2.2 About the IEEE-754 Standard                                   | 3   |

| 2.2.1 Single precision format                                     | 3   |

| 2.2.2 Subnormal numbers                                           | 4   |

| 2.2.3 NaNs (not a numbers)                                        | 4   |

| 2.3 About RISC-V's "F" Single Precision Float Extension           | 4   |

| 2.4 About Spike and RISCV-DV                                      | 5   |

| 2.4.1 Spike                                                       | 5   |

| 2.4.2 RISCV-DV                                                    | 6   |

| 2.5 About Basics of Artificial Neural Networks                    | 7   |

| 2.5.1 Neural networks                                             | 7   |

| 2.5.2 Mathematical foundations                                    | 8   |

| 2.5.3 Activation functions                                        | 9   |

| 2.5.3.1 ReLU (rectified linear unit) function                     | 9   |

| 2.5.3.2 Softmax function                                          | 9   |

| ${\bf 3.\ A\ UNIVERSAL\ VERIFICATION\ METHODOLOGY\ ENVIRONMENT\}$ | 11  |

| 3.1 What is Universal Verification Methodology                    | 11  |

| 3.2 Basic UVM Testbench Structure                                 | 11  |

| 3.2.1 Sequence item and interface                                 | 12  |

| 3.2.2 Sequencer                                                   | 14  |

| 3.2.3 Driver                                                      | 15  |

| 3.2.4 Monitor                                                     | 16  |

| 3.2.5 Agent                                                       | 17  |

| 3.2.6 Scoreboard                                                  | 19  |

| 3.2.7 Environment                                                 | 21  |

| 3.2 8 Test                                                        | 22  |

|    | 3.2.9 Testbench                                      | 24  |

|----|------------------------------------------------------|-----|

|    | 3.2.10Adder module                                   | 25  |

|    | 3.3 UVM Factory                                      | 29  |

|    | 3.4 Basic UVM Macros Used in Adder Verification      | 29  |

|    | 3.4.1 uvm_component_utils                            | 29  |

|    | 3.4.2 uvm_object_utils                               | 30  |

|    | 3.4.3 uvm_fatal                                      | 30  |

|    | 3.4.4 uvm_info                                       | 30  |

|    | 3.4.5 uvm_error                                      | 31  |

|    | 3.5 UVM Testbench Results                            | 31  |

| 4. | IBEX VERIFICATION ENVIRONMENT                        | 33  |

|    | 4.1 Getting the Ibex Environment Running             | 33  |

|    | 4.1.1 Initial attempt                                | 33  |

|    | 4.1.2 Trying to obtain a working environment         | 34  |

|    | 4.2 Setting Up and Analyzing the Environment         | 35  |

|    | 4.2.1 Setup of the environment                       | 35  |

|    | 4.2.2 Analyzing the environment                      | 40  |

|    | 4.3 Connecting Hornet to the Environment             | 44  |

|    | 4.4 Technical Difficulties                           | 49  |

| 5. | CUSTOM VERIFICATION ENVIRONMENT                      | 51  |

|    | 5.1 Manual Fixes on Hornet                           | 51  |

|    | 5.1.1 Increasing the memory                          | 51  |

|    | 5.1.2 Fixes relating to the verification environment | 52  |

|    | 5.1.3 Preliminary FPU fixes                          | 53  |

|    | 5.1.3.1 Some basic tests for edge cases              | 53  |

|    | 5.1.3.2 Test on digital filter                       | 57  |

|    | 5.1.3.3 Test on "Paranoia"                           | 59  |

|    | 5.2 Creating a New Verification Environment          | 62  |

|    | 5.2.1 Hornet tracer                                  |     |

|    | 5.2.2 Automating the environment                     |     |

|    | 5.2.2.1 Automatically exiting the program            | 69  |

|    | 5.2.2.2 RISCV-DV                                     |     |

|    | 5.2.2.3 Log parsing and comparison scripts           |     |

|    | 5.2.2.4 Main script                                  |     |

| 6. | FIXING HORNET USING THE ENVIRONMENT                  |     |

|    | 6.1 Non-FPU Fixes                                    |     |

|    | 6.2 FPU Fixes                                        |     |

|    | 6.2.1 Edge cases                                     |     |

|    | 6.2.2 Rounding fixes                                 |     |

|    | 6.2.3 Fixing insufficient precision issues           |     |

| 7. | AI APPLICATION AS A BENCHMARK                        |     |

|    | 7.1 Training the Model Using TensorFlow              |     |

|    | 7.2 Running the Model on the Hornet Core             |     |

| 8. | REALISTIC CONSTRAINTS AND CONCLUSIONS                |     |

|    | 8.1 Practical Application of this Project            | 101 |

| 8.2 Realistic Constraints                       | 101 |

|-------------------------------------------------|-----|

| 8.2.1 Social, environmental and economic impact | 101 |

| 8.2.2 Cost analysis                             | 101 |

| 8.2.3 Standards                                 | 101 |

| 8.2.4 Health and safety concerns                | 101 |

| 8.3 Future Work and Recommendations             | 102 |

| REFERENCES                                      | 103 |

#### **ABBREVIATIONS**

**AI** : Artificial Intelligence

**ISA** : Instruction Set Architecture

**ReLU** : Rectified Linear Unit

**IEEE**: Institute of Electrical and Electronics Engineers

NaN : Not a Number

MLP : Multi Layer Perceptron

**UVM** : Universal Verification Methodology

OOP : Object Oriented Programming

DUT : Design Under TestMLP : Multi Layer PerceptronGUI : Graphical User Interface

CSR : Control and Status Register

**FPU**: Floating Point Unit

**SQRT** : Square Root

MDS : Multiply-Divide-Square RootRAM : Random Access MemoryROM : Read Only Memory

RTL : Register Transfer Level

WSL : Windows Subsystem for LinuxRNE : Round to Nearest, ties to Even

**RTZ** : Round Towards Zero

RDN : Round Down RUP : Round Up

**RMM**: Round to Nearest, Ties to Maximum Magnitude

**DYN**: Dynamic Mode

G Bit : Guard Bit

R Bit : Rounding Bit

S Bit : Sticky Bit

MNIST : Modified National Institute of Standards and Technology

# LIST OF TABLES

|           |   | <u>P</u>                               | age |

|-----------|---|----------------------------------------|-----|

| Table 2.1 | : | Instructions of 'F' standard extension | 5   |

| Table 4.1 | : | File descriptions and their purposes.  | 36  |

| Table 6.1 | : | Rounding mode encoding of RISC-V [1].  | 83  |

# LIST OF FIGURES

|            |   | $\mathbf{P}_{\mathbf{i}}$                                        | age |

|------------|---|------------------------------------------------------------------|-----|

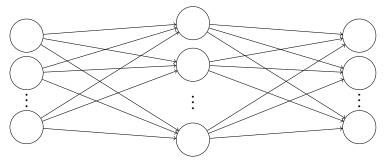

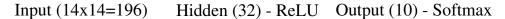

| Figure 2.1 | : | Illustration of a basic neural network.                          | 8   |

| _          |   | General UVM architecture [2]                                     |     |

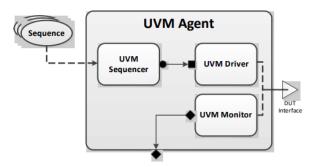

| Figure 3.2 | : | Agent structure [2]                                              | 18  |

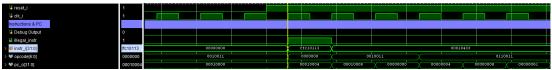

| Figure 3.3 | : | UVM testbench start                                              | 31  |

| Figure 3.4 | : | PASS messages coming from the scoreboard                         | 32  |

| Figure 3.5 | : | UVM report summary for the correct adder module                  | 32  |

| Figure 3.6 | : | ERROR messages coming from the scoreboard                        | 32  |

| Figure 3.7 | : | UVM report summary for the incorrect adder module                | 32  |

| Figure 4.1 | : | Terminal output for successful Ibex Verification.                | 37  |

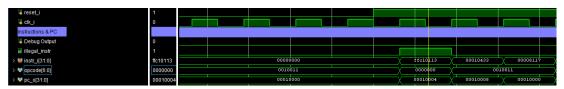

| Figure 5.1 | : | The operation of the core before the fix.                        | 53  |

| Figure 5.2 | : | The operation of the core after the fix.                         | 53  |

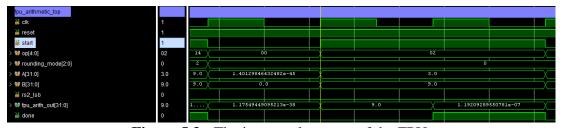

| Figure 5.3 | : | The input and outputs of the FPU                                 | 61  |

| Figure 5.4 | : | The states that govern the Multiply-Divide-SQRT unit operation   | 62  |

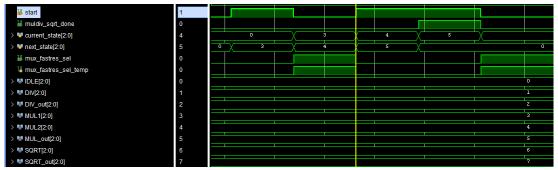

| Figure 6.1 | : | Wasted algorithm cycles. Note that, for several cycles after the |     |

|            |   | start signal is given, signal sq_root is unchanged               | 90  |

| Figure 7.1 | : | Basic MLP model designed to detect digits.                       | 95  |

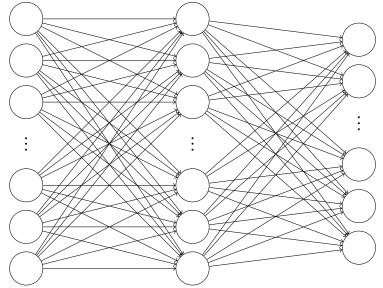

| Figure 7.2 | : | Some digits from MNIST dataset that are reduced to 14x14 pixels  | 96  |

| Figure 7.3 | : | Comparison result of MLP model.                                  | 99  |

#### **SUMMARY**

In this project, the main goal was to create a reusable and scalable verification environment for RISC-V processors. The Hornet core, designed at Istanbul Technical University (ITU), was selected as the main processor for verification. Hornet mainly supports integer arithmetic and multiplication/division operations. It was later extended to support single precision floating point operations. Since RISC-V is an open-source instruction set architecture, it enables universities and research groups to design their own cores. However, the lack of open-source and general-purpose verification systems for floating point RISC-V cores limits this potential. This project focused on solving this problem by building an adaptable, open-source verification system. Spike was used as a reference software simulator to execute RISC-V instructions and check behavior. RISCV-DV was used to generate random test cases to evaluate how the processor behaves under many different input conditions.

The Ibex verification environment was also studied. Ibex is another open-source RISC-V core with an existing UVM-based testbench. To use this environment, multiple setup issues were resolved. The required simulation tools and RISC-V toolchain did not exist in ITU's laboratories. Therefore, a new simulator program named QuestaSim was used via a company named Electra IC's servers. To do this, several configuration changes needed to be made. After that, floating point test support was added by modifying instruction generation settings and writing a custom test configuration. Unfortunately, server access was later shut down due to technical issues. This part of the work helped in understanding RISCV-DV in general.

Before searching for a new environment, several manual fixes were applied to Hornet to improve memory usage and address floating point unit problems. Later, a new custom verification environment was created for Hornet. A tracing system was added to monitor instruction-level behavior during execution to be used in the new environment. This environment was designed to use Python to generate random instructions and to compare RTL-level results with Spike results. Edge behaviors, such as rounding, subnormal numbers, and NaN cases, were evaluated. To automate the process, scripts were created to generate programs, run simulations, parse logs, and compare outputs. These scripts made it possible to automatically detect mismatches which means that there is an error. This environment was built to work with widely used open-source tools such as RISCV-DV, Spike, and Python. A main script was added to manage the entire process, from code generation to result checking. This made the verification process much easier to repeat and reuse for future designs. Using this environment, many changes were made both in the FPU and in Hornet itself.

After fixing errors, it was desired to show that the verification system could support realistic applications such as a simple artificial neural network. A multilayer

perceptron model was trained using TensorFlow to recognize handwritten digits. This model was later adapted and executed on Hornet. Environment results showed that the processor was able to run the neural network correctly. This confirmed that Hornet can now be considered a fully functional open-source RV32IMF core.

In conclusion, an open-source, flexible, and automated verification environment was successfully built for testing Hornet. It enabled efficient error detection and supported real-world applications, making it a useful framework for both academic and industrial research.

### ÖZET

Bu projede temel amaç, RISC-V işlemcileri için tekrar kullanılabilir ve ölçeklenebilir bir doğrulama ortamı oluşturmaktı. İstanbul Teknik Üniversitesi (İTÜ) tarafından tasarlanan Hornet çekirdeği, doğrulama işlemi için ana işlemci olarak seçildi. Hornet, temel olarak tam sayı aritmetiği ve çarpma/bölme işlemlerini desteklemektedir. Daha sonra, tek duyarlıklı kayan nokta aritmetiğini destekleyecek şekilde genişletilmiştir. RISC-V açık kaynaklı bir komut seti mimarisi olduğu için, üniversiteler ve araştırma grupları kendi çekirdeklerini tasarlayabilmektedir. Ancak kayan nokta aritmetiği destekli RISC-V çekirdekleri için genel amaçlı ve açık kaynaklı doğrulama sistemlerinin eksikliği, bu potansiyeli sınırlamaktadır. Bu proje, uyarlanabilir ve açık kaynaklı bir doğrulama sistemi oluşturarak bu sorunu çözmeyi hedeflemiştir. Spike, RISC-V komutlarını çalıştırmak ve davranışı kontrol etmek için referans yazılım simülatörü olarak kullanılmıştır. RISCV-DV ise işlemcinin farklı giriş koşullarındaki davranışını değerlendirmek için rastgele test senaryoları üretmekte kullanılmıştır.

Ibex doğrulama ortamı da incelenmiştir. Ibex, halihazırda UVM tabanlı bir testbench'e sahip olan başka bir açık kaynaklı RISC-V çekirdeğidir. Bu ortamı kullanmak için çeşitli kurulum sorunları çözülmüştür. İTÜ laboratuvarlarında gerekli simülasyon araçları ve RISC-V toolchain mevcut değildi. Bu nedenle, Electra IC adlı bir şirketin sunucuları üzerinden QuestaSim isimli bir simülatör programı kullanılmıştır. Bu işlemi gerçekleştirmek için bazı yapılandırma dosyalarında değişiklik yapılması gerekmiştir. Sonrasında, kayan nokta aritmetiği testi desteği sağlamak amacıyla talimat üretim ayarları değiştirilmiş ve özel bir test konfigürasyonu yazılmıştır. Ancak daha sonra, teknik sorunlar nedeniyle sunucu erişimi kapatılmıştır. Bu süreç, genel olarak RISCV-DV'nin nasıl çalıştığını anlamaya katkı sağlamıştır.

Yeni bir ortam arayışına başlamadan önce, Hornet üzerinde çeşitli manuel düzeltmeler yapılmıştır. Bu düzeltmeler, bellek kullanımıyla ilgili iyileştirmeler ve kayan nokta birimiyle ilgili sorunların giderilmesi amacıyla gerçekleştirilmiştir. Daha sonra, Hornet için özel bir doğrulama ortamı oluşturulmuştur. Bu yeni ortamda kullanılmak üzere, komut düzeyindeki işlem davranışını izleyebilen bir tracer sistemi eklenmiştir. Ortam, rastgele komut üretmek için Python kullanacak ve RTL düzeyindeki sonuçları Spike çıktılarıyla karşılaştıracak şekilde tasarlanmıştır. Yuvarlama, subnormal sayılar ve NaN durumları gibi uç durumlar değerlendirilmiştir. Doğrulama sürecini otomatikleştirmek için program üretimi, simülasyon çalıştırma, log dosyalarını ayrıştırma ve sonuç karşılaştırma işlemlerini yöneten scriptler yazılmıştır. Bu scriptler sayesinde hataya işaret eden uyuşmazlıklar otomatik olarak tespit edilebilmiştir. Ortam, RISCV-DV, Spike ve Python gibi yaygın açık kaynak araçlarla çalışacak şekilde inşa edilmiştir. Sürecin tamamını kod üretiminden sonuç kontrolüne kadar yöneten bir script eklenmiştir. Bu sayede doğrulama işlemi tekrar edilebilir ve gelecek

tasarımlar için yeniden kullanılabilir hale gelmiştir. Bu ortam kullanılarak hem FPU'da hem de Hornet üzerinde birçok değişiklik yapılmıştır.

Hatalar giderildikten sonra, doğrulama sisteminin gerçekçi uygulamaları destekleyip desteklemediğini göstermek amaçlanmıştır. Bu doğrultuda, basit bir yapay sinir ağı örneği test edilmiştir. El yazısı rakamları tanımak üzere TensorFlow kullanılarak bir multilayer perceptron modeli eğitilmiştir. Bu model, Hornet üzerinde çalıştırılmak üzere uyarlanmış ve simülasyon ortamında test edilmiştir. Ortamdan elde edilen sonuçlar, işlemcinin sinir ağını doğru şekilde çalıştırabildiğini göstermiştir. Böylece Hornet'in artık tam işlevsel, açık kaynaklı bir RV32IMF çekirdeği olarak değerlendirilebileceği doğrulanmıştır.

Sonuç olarak, Hornet'in doğrulanması için açık kaynaklı, esnek ve otomatik bir doğrulama ortamı başarıyla oluşturulmuştur. Bu ortam, hataların etkin bir şekilde tespit edilmesini sağlamış ve gerçek dünya uygulamalarını destekleyerek hem akademik hem de endüstriyel araştırmalar için kullanışlı bir çerçeve sunmuştur.

#### 1. INTRODUCTION

### 1.1 Purpose of the Project

The verification of RISC-V processors faces challenges due to bespoke solutions tailored for specific cores, limiting scalability and adaptability. This creates a bottleneck for developers, particularly in validating processors with advanced instruction sets like RV32IMF for floating-point operations, which are critical for AI applications. Current methods are inefficient for diverse core designs, hindering broader adoption. This project addresses these issues by developing a modular, scalable, and reusable verification environment to ensure compliance with RISC-V standards, detect errors, and enable seamless integration into computationally demanding tasks, fulfilling a need for researchers and companies.

#### 1.2 Literature Review

Current solutions for RISC-V core verification include tools and frameworks designed for specific needs but with notable limitations. The Ibex verification environment [3] is tailored for the Ibex core, offering precise validation but requiring extensive effort to adapt to other cores. Similarly, RISCV-DV [4] provides a strong foundation with its random instruction generation capabilities, yet it requires additional integration effort for hardware validation in diverse core designs. ITU's Hornet [5], supporting the RV32IM instruction set, demonstrates academic advancements in RISC-V core design. Extensions to Hornet, such as the F extension for floating point operations [6], emphasize the need for robust validation in floating point computation, a critical area for AI workloads. The RISC-V Instruction Set Architecture (ISA) specification [1] provides the foundational standards for compliance in all RISC-V cores. Tools like Spike, the RISC-V ISA Simulator [7], are used as reference models to verify compliance. However, Spike's focus on simulation limits its capability to address real-time validation needs in hardware. The proposed solution builds upon the

strengths of these existing tools and standards while addressing their limitations. By creating a scalable and modular verification framework, this project supports compliance across multiple cores, enables advanced feature validation, and facilitates practical applications such as AI workloads.

#### 2. BACKGROUND INFORMATION

#### 2.1 About RISC-V and Hornet

RISC-V is an open-source instruction set architecture created by researchers at the University of California, Berkeley, for teaching and research use [1]. Later, it became more popular and is now used around the world. Its open design also helps universities and companies create their own custom processors. At the same time, it is flexible and can grow to support many types of applications. In addition, Hornet is a 32-bit processor that supports the I and M instruction sets meaning that it can process basic integer arithmetic and multiplication and division. It was designed by students from Istanbul Technical University [5]. Later, it was updated to have the F extension, meaning that it has support to perform operations using floating point numbers [6].

#### 2.2 About the IEEE-754 Standard

IEEE-754 is a standard for floating point numbers made by the IEEE (Institute of Electrical and Electronics Engineers) [8]. It is used in many processors. The standard helps to store and calculate decimal numbers in binary form. It is useful for science, engineering, and graphics. In this standard, there are different formats, such as single precision and double precision. However, Hornet only supports single precision floating point numbers.

## 2.2.1 Single precision format

In single precision, a number has 32 bits. The first bit is the sign bit. It shows if the number is positive or negative. The next 8 bits are the exponent. The last 23 bits are the mantissa. The real value of the number is calculated with this formula  $(-1)^{\text{sign}} \times 1$ .mantissa  $\times 2^{(\text{exponent}-127)}$ . This formula is used when the number is a normal value.

#### 2.2.2 Subnormal numbers

Subnormal numbers are very small numbers close to zero. They are used when the exponent is zero and the mantissa is not zero. In this case, the formula becomes  $(-1)^{\text{sign}} \times 0$ .mantissa  $\times 2^{-126}$ . Subnormal numbers help avoid sudden jumps from zero to normal values. They give smooth results near zero.

#### 2.2.3 NaNs (not a numbers)

NaN means "Not a Number." It shows up when a calculation has no real answer, like dividing 0 by 0. There are two types of NaN:

- Quiet NaN: This type does not stop the program. It gives NaN as a result. The program continues to run.

- **Signaling NaN:** This type causes an error or warning. It tells the program that something is wrong.

The difference between them is in one special bit in the mantissa.

# 2.3 About RISC-V's "F" Single Precision Float Extension

The F extension in RISC-V [9] adds support for floating-point operations. These operations work with decimal numbers using special registers. The extension follows the IEEE 754 standard. It allows the processor to do math like addition, subtraction, multiplication, and division with floating-point numbers. There are also instructions to move data between integer and floating-point registers. Some instructions check if two values are equal or compare their sizes. Other instructions help convert between integer and floating-point formats. All instructions in the F extension are listed and explained in the Table 2.1. One important thing to mention is that the Hornet Core does not have fused instructions FMADD.S, FMSUB.S, FNMADD.S and FNMSUB.S implemented as mentioned in [6]. Therefore, -ffp-contract=off is used while the compiling to tell the compiler to not use them.

**Table 2.1**: Instructions of 'F' standard extension.

| Instructions        | <b>Executing Operations</b>                                                                                 |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| FLW, FSW            | Loads/Stores Floating-point data to/from destination.                                                       |

| FMADD.S, FMSUB.S    | Multiplies source1, source2, adds source3, stores in destination.                                           |

| FNMADD.S,           | Multiplies source1, source2, negates, adds source3,                                                         |

| FNMSUB.S            | stores in destination.                                                                                      |

| FADD.S, FSUB.S,     | Adds/Subtracts/Multiplies/Divides source1, source2,                                                         |

| FMUL.S, FDIV.S      | stores in destination.                                                                                      |

| FSQRT.S             | Computes square root of source1, stores in destination.                                                     |

|                     | Takes all bits from source1 except sign bit, which is                                                       |

| FSGNJ.S, FSGNJN.S,  | determined by the sign of source2, the opposite sign                                                        |

| FSGNJX.S            | of source2, or XOR of signs of source1 and source2,                                                         |

|                     | stores in destination.                                                                                      |

| FMIN.S, FMAX.S      | Takes min/max of source1 and source2, stores in destination.                                                |

| FCVT.W.S,           | Converts floating-point source1 value to signed/unsigned                                                    |

| FCVT.WU.S           | integer value, stores in destination.                                                                       |

| FMV.X.W, FMV.W.X    | Moves floating-point value from source1 to lower 32 bits of integer register destination, or vice versa.    |

| FEQ.S, FLT.S, FLE.S | Equality/Less than/Less than or equal to of source1, source2, stores in destination.                        |

| FCLASS.S            | Examines value in source1, stores 10-bit mask in destination that indicates class of floating-point number. |

| FCVT.S.W,           | Converts signed/unsigned source1 value to floating-point                                                    |

| FCVT.S.WU           | value, stores in destination.                                                                               |

# 2.4 About Spike and RISCV-DV

The main environment uses the Spike and RISCV-DV as core programs to compare the results to see if they works as expected and to generate random tests.

# 2.4.1 Spike

Spike is a software tool that simulates a RISC-V processor. It is called instruction set simulator. It runs RISC-V programs and shows how the processor works step by step. It is very useful for testing and debugging software before running it on real hardware.

Spike is often used by researchers and developers to check if their cores are working correctly. It supports different instruction sets. In this project, we use the RV32IMF instruction set since the Hornet was designed to be.

A sample command to run Spike is shown below:

```

spike --log-commits --isa=rv32imf --priv=M \

-m0xf000:1,0x10000:0x8000,0x8010:1 -1 \

--log=spike.log ${TEST}.elf

```

This command starts Spike with the following settings:

- -log-commits records each instruction.

- -isa=rv32imf sets the instruction set to RV32IMF.

- -priv=M means machine mode is used.

- -m... defines memory regions for the simulation.

- -1 enables logging to the terminal.

- -log=spike.log saves the log in a file.

- \$TEST.elf is the test program to run.

## 2.4.2 RISCV-DV

RISCV-DV is a test generation tool for RISC-V processors. It creates random instruction tests to check if the processor behaves correctly. It is often used during processor design and verification. The tool specifically uses some corner cases that are hard to catch with normal tests.

RISCV-DV supports many RISC-V extensions, including the floating point F extension. It works with simulation tools like Spike. It is written in Python and can be run using the command line.

A basic command to run a test with RISCV-DV is:

```

run.py --verbose --test ${TEST} --simulator pyflow \

--isa rv32imf --mabi ilp32f --sim_opts=""

```

This command does the following:

• -verbose prints more details while running.

- -test \$TEST selects the test name.

- -simulator pyflow sets the simulator.

- -isa rv32imf sets the instruction set.

- -mabi ilp32f sets the memory ABI for floating point.

- -sim\_opts="" sets simulator options (empty here).

After running this command, it generates the assembly code, compiles it, and runs the simulation. The results can then be checked for errors or unexpected behavior.

#### 2.5 About Basics of Artificial Neural Networks

Neural networks are not taking a big part in this project. However, it was used as an example application to show that the project works as expected in Chapter 7.

#### 2.5.1 Neural networks

Artificial Neural Networks are computational models that are designed to behave like the biological neural systems. They create a network with connected units called neurons. When neurons receives inputs, it applies a weighted matrix to it, and the result goes through a function called activation function. The result of the activation functions are given to the next layer.

Neural networks are widely used across the scientific community for the purposes involving pattern recognition, classification, regression and approximation of functions that are incapable to solve analytically. The neural networks can be as basic as just a few neurons to big complex multilayer networks.

Training of a neural network is done by calculating its weights using a dataset and a learning algorithm. Neural networks are powerful because they are able to learn from data and generalize these data without almost no problem. This is the reason why it is used widely.

### 2.5.2 Mathematical foundations

Figure 2.1: Illustration of a basic neural network.

Assume a neural network with one hidden layer, which means that it has one layer between output and input layer. Such a neural network is called multilayer perceptron or MLP as it has more than 1 layers. It can be seen in Figure 2.1. Let:

- $\mathbf{x} \in \mathbb{R}^n$ : input vector

- $\mathbf{W}^{(1)} \in \mathbb{R}^{h \times n}$ : weight matrix from input to hidden layer

- $\mathbf{b}^{(1)} \in \mathbb{R}^h$ : bias vector for hidden layer

- $\phi(\cdot)$ : activation function for hidden layer

- $\mathbf{W}^{(2)} \in \mathbb{R}^{m \times h}$ : weight matrix from hidden to output layer

- $\mathbf{b}^{(2)} \in \mathbb{R}^m$ : bias vector for output layer

- $f(\cdot)$ : output activation function

The computations of the MLP are as follows:

$$\mathbf{z}^{(1)} = \mathbf{W}^{(1)}\mathbf{x} + \mathbf{b}^{(1)}$$

$$\mathbf{a}^{(1)} = \phi(\mathbf{z}^{(1)})$$

$$\mathbf{z}^{(2)} = \mathbf{W}^{(2)}\mathbf{a}^{(1)} + \mathbf{b}^{(2)}$$

$$\mathbf{y} = f(\mathbf{z}^{(2)})$$

The model is trained using gradient descent and backpropagation. The loss function  $\mathcal{L}(\hat{\mathbf{y}}, \mathbf{y})$  measures the error between prediction and truth. The weights are updated using:

$$\theta \leftarrow \theta - \eta \nabla_{\theta} \mathscr{L}$$

where  $\eta$  is the learning rate.

#### 2.5.3 Activation functions

There are a lot of activation functions used in the context of artificial networks. However, only two are used in this project named ReLU (rectified linear unit) and softmax function.

## 2.5.3.1 ReLU (rectified linear unit) function

The ReLU activation function is defined as:

$$ReLU(x) = max(0, x)$$

Its derivative is:

$$\frac{d}{dx} \operatorname{ReLU}(x) = \begin{cases} 1 & \text{if } x > 0 \\ 0 & \text{if } x \le 0 \end{cases}$$

#### 2.5.3.2 Softmax function

The Softmax function for a vector  $\mathbf{z} = [z_1, z_2, \dots, z_K]$  is defined as:

Softmax

$$(z_i) = \frac{e^{z_i}}{\sum_{j=1}^K e^{z_j}}, \quad \text{for } i = 1, 2, \dots, K$$

Its derivative is:

$$\frac{\partial \operatorname{Softmax}(z_i)}{\partial z_j} = \operatorname{Softmax}(z_i)(\delta_{ij} - \operatorname{Softmax}(z_j))$$

#### 3. A UNIVERSAL VERIFICATION METHODOLOGY ENVIRONMENT

## 3.1 What is Universal Verification Methodology

In modern digital design, verifying a circuit before manufacturing is essential. The Universal Verification Methodology (UVM) is a widely used framework that helps engineers test complex hardware designs in a structured and reusable way. To understand how UVM works an 8-bit adder is verified.

UVM uses object-oriented programming (OOP) principles to create a testbench that interacts with the Device Under Test (DUT). Instead of manually writing multiple test cases, UVM provides an automated approach to generate inputs, monitor outputs, and compare results.

### 3.2 Basic UVM Testbench Structure

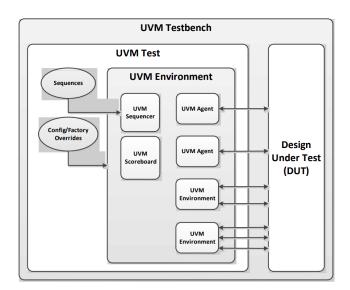

A UVM testbench consists of several key components, each responsible for a specific part of the verification process. The main modules and their functions are described below. A general architecture can be seen in Figure 3.1.

**Figure 3.1**: General UVM architecture [2].

### 3.2.1 Sequence item and interface

In UVM-based verification, the interface (adder\_if) and sequence item (adder\_tx) are essential components that facilitate structured and efficient communication between the testbench and the DUT.

The interface (adder\_if) acts as a connection between the DUT and the UVM testbench. It groups the DUT's input and output signals in a single construct, making it easier for multiple testbench components, such as the driver and monitor, to interact with the DUT without directly accessing its ports. The adder\_if includes a clock signal (clk), a reset signal (rst), two 8-bit inputs (x and y), and a 9-bit output (out). Additionally, it contains a clocking block (cb) that ensures synchronized signal interaction. The clocking block specifies which signals are read and which signals are driven, ensuring that the testbench applies input data and captures output data at the correct time in the simulation.

```

import uvm_pkg::*;

include "uvm_macros.svh"

interface adder_if(input bit clk);

logic rst;

logic [7:0] x;

logic [7:0] y;

logic [8:0] out;

clocking cb @(posedge clk);

input rst;

input out;

output x;

output y;

endclocking

endinterface

```

The sequence item (adder\_tx) represents a single transaction that is sent to the DUT. In UVM, a transaction is an object that contains the necessary data to stimulate the DUT. The adder\_tx class extends uvm\_sequence\_item, meaning it serves as the basic unit of communication between the sequencer and the driver. It defines two randomized 8-bit input values and a 9-bit output. The constraint block ensures that the inputs stay within the range of 0 to 255, preventing unexpected

behavior. Additionally, the convert2str() function formats the transaction data into a string.

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class adder_tx extends uvm_sequence_item;

`uvm_object_utils(adder_tx)

rand bit [7:0] x, y; //Inputs

bit [8:0] out;

//Output

//Constraining input values

constraint valid range {

x inside {[0:255]};

y inside {[0:255]};

function new(string name = "adder_tx");

super.new(name);

endfunction

virtual function string convert2str();

return $sformatf("x=%0d, y=%0d, sum=%0d", x, y, out);

endfunction

endclass

```

The interface and sequence item work together in the UVM testbench to generate test scenarios and apply them to the DUT. The sequencer creates multiple  $adder_tx$  transactions, each containing random values of x and y. The driver retrieves these transactions from the sequencer and assigns them to the DUT's input signals using  $adder_if$ . After the DUT processes the inputs, the monitor captures the output using the interface and sends the transaction data to the scoreboard for verification.

By using an interface for signal communication and a sequence item for structured transactions, UVM enables efficient and reusable verification. This approach ensures that testbench components remain modular and can interact with the DUT without direct dependencies, leading to a more scalable and maintainable verification environment.

## 3.2.2 Sequencer

This UVM sequence (gen\_item\_seq) class is responsible for generating and sending transactions to the sequencer, which then forwards them to the driver for execution on the DUT. The class defines a random variable (num) that determines how many transactions will be generated, constrained between 10 and 50. In the body() task, the sequence creates transaction objects (adder\_tx), randomizes their values, and sends them to the driver using start\_item() and finish\_item(). If randomization fails, an error message is logged. This kind of error checking is important in UVM since it makes the project easy to debug. Sequences are responsible for generating transaction-level stimuli, while the sequencer acts as a middleman, managing the flow of these transactions to the driver. If multiple sequences are used, the sequencer will schedule them based on arbitration policies, meaning transactions can be interleaved or prioritized depending on configuration. This allows for parallel testing scenarios, improving verification coverage.

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class gen_item_seq extends uvm_sequence;

`uvm_object_utils(gen_item_seq)

function new(string name = "gen_item_seq");

super.new(name);

endfunction

rand int num;

constraint c1 {soft num inside {[10:50]};}

//Body: Generates and randomizes multiple transactions

virtual task body();

for (int i = 0; i < num; i++) begin</pre>

adder_tx m_item = adder_tx::type_id::create("m_item");

start_item(m_item);

if (!m_item.randomize())

`uvm_error("SEQ", "Randomization failed for m_item!");

`uvm_info("SEQ", $sformatf("Generate new item: %s",

m_item.convert2str()), UVM_HIGH);

```

### **3.2.3 Driver**

The UVM driver class is responsible for receiving transactions from the sequencer and applying them to the DUT through the virtual interface (vif). The build\_phase() retrieves the virtual interface from the UVM configuration database and reports a fatal error if it is not found. The run\_phase() runs indefinitely, waiting for transactions from the sequencer using get\_next\_item(), then calls drive\_item() to apply the input values (x and y) to the DUT. The drive\_item() task synchronizes with the DUT's interface using the clocking block (vif.cb) and assigns the transaction values to the interface signals. This setup ensures that the generated test data flows correctly from the sequencer to the DUT, enabling effective stimulus application.

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class driver extends uvm_driver #(adder_tx);

`uvm_component_utils(driver)

function new(string name = "driver", uvm_component parent=null);

super.new(name, parent);

endfunction

virtual adder_if vif;

/*Build phase: Retrieves the virtual interface from

the UVM configuration database*/

virtual function void build_phase(uvm_phase phase);

if (!uvm_config_db#(virtual adder_if)::get(this, "",

"adder_vif", vif))

`uvm_fatal("DRV", "Could not get vif");

endfunction

//Run phase: Waits for transactions and sends them to the DUT

virtual task run_phase(uvm_phase phase);

```

```

super.run_phase(phase);

forever begin

adder_tx m_item;

`uvm_info("DRV",

$sformatf("Wait for item from sequencer"), "UVM_HIGH")

seq_item_port.get_next_item(m_item);

drive_item(m_item);

seq_item_port.item_done();

end

endtask

/*Drive item: Applies transaction values to the DUT

through the virtual interface */

virtual task drive_item(adder_tx m_item);

@(vif.cb);

vif.cb.x <= m_item.x;</pre>

vif.cb.y <= m_item.y;</pre>

endtask

endclass

```

#### 3.2.4 Monitor

The UVM monitor class is responsible for observing the DUT signals and forwarding them to other components, such as the scoreboard, for verification. The build\_phase() retrieves the virtual interface (vif) from the UVM configuration database and initializes the analysis port (mon\_analysis\_port), which is used to send collected transactions to other components. The run\_phase() runs continuously, waiting for DUT signal changes using the clocking block (vif.cb). It captures the input values and the output from the DUT, creates a new transaction object (adder\_tx), and sends it through the analysis port. If reset is active, it skips capturing data. This ensures that every transaction processed by the DUT is observed and logged, enabling the scoreboard to check for correctness.

```

import uvm_pkg::*;

include "uvm_macros.svh"

import tb_pkg::*;

class monitor extends uvm_monitor;

`uvm_component_utils(monitor)

function new(string name="monitor", uvm_component parent=null);

```

```

super.new(name, parent);

endfunction

uvm_analysis_port #(adder_tx) mon_analysis_port;

virtual adder_if vif;

/*Build phase: Retrieves the virtual interface

and initializes the analysis port*/

virtual function void build_phase(uvm_phase phase);

super.build phase (phase);

if (!uvm_config_db#(virtual adder_if)::get(this, "",

"adder_vif", vif))

`uvm_fatal("MON", "Could not get vif")

mon_analysis_port = new ("mon_analysis_port", this);

endfunction

/*Run phase: Monitors DUT signals and sends

transactions through the analysis port*/

virtual task run_phase(uvm_phase phase);

super.run_phase(phase);

forever begin

@ (vif.cb);

if(!vif.rst) begin

adder_tx item=adder_tx::type_id::create("item");

item.x = vif.x;

item.y = vif.y;

item.out = vif.cb.out;

mon_analysis_port.write(item);

`uvm_info("MON", $sformatf("Saw item %s",

item.convert2str()), UVM_HIGH)

end

end

endtask

endclass

```

## **3.2.5** Agent

The UVM agent class in this code serves as a container for the driver (d0), monitor (m0), and sequencer (s0). The agent is responsible for handling the transaction flow between the sequencer and the DUT. The build\_phase() is responsible for creating instances of the sequencer, monitor, and driver using the UVM factory. The connect\_phase() ensures that the driver is connected to the sequencer, allowing the driver to receive transaction items generated by sequences. This setup ensures that

input data flows correctly from the sequencer to the driver, while the monitor observes the DUT behavior and sends transaction data to other testbench components.

Multiple agents are used when the DUT has multiple interfaces or communication channels that need independent verification. Each agent is responsible for managing transactions on a specific interface, ensuring modularity and scalability in the testbench. Agents contain a sequencer, driver, and monitor, which work together to generate, apply, and observe transactions.

When multiple agents are present, each agent operates independently, processing its own set of transactions. The sequencer in each agent generates stimulus, and the driver applies these stimuli to different parts of the DUT. Meanwhile, the monitors capture DUT responses and send them to the scoreboard for validation. If the agents interact with shared DUT resources, arbitration mechanisms may be required to handle potential conflicts.

Having multiple agents allows the testbench to verify parallel data paths, master-slave architectures, or multi-protocol communication. For example, in a bus-based design, one agent may act as a master generating read/write requests, while another agent acts as a slave responding to those transactions. This enables a realistic verification of complex DUT behaviors, ensuring that different functional blocks operate correctly together.

Figure 3.2 : Agent structure [2].

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class agent extends uvm_agent;

`uvm_component_utils(agent)

```

```

function new(string name = "agent", uvm_component parent=null);

super.new(name, parent);

endfunction

driver d0;

monitor m0;

uvm_sequencer #(adder_tx) s0;

//Build phase: Creates instances of the sequencer,

monitor, and driver*/

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

s0 = uvm_sequencer#(adder_tx)::type_id::create("s0", this);

m0 = monitor::type_id::create("m0", this);

d0 = driver::type_id::create("d0", this);

endfunction

//Connect phase: Connects the driver to the sequencer

virtual function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

d0.seg item port.connect(s0.seg item export);

endfunction

endclass

```

## 3.2.6 Scoreboard

The UVM scoreboard class is responsible for checking the correctness of DUT outputs by comparing them with expected values. The build\_phase() initializes the analysis import port (m\_analysis\_imp), which receives transaction data from the monitor. The write() function computes the expected output (expected\_value) by adding x and y from the transaction and stores it in a queue (exp\_out\_queue). Since the DUT has a 1-clock delay, the scoreboard waits until at least one previous expected value is available before comparing the actual output (item.out) with the delayed expected output (delayed\_exp\_out). If the values match, a PASS message is logged; otherwise, an ERROR message is generated. This ensures that verification accounts for timing delays in the DUT, preventing incorrect failures due to mismatched comparisons.

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class scoreboard extends uvm_scoreboard;

`uvm_component_utils(scoreboard)

function new(string name="scoreboard", uvm_component parent=null);

super.new(name, parent);

endfunction

bit [8:0] exp_out_queue[$];

bit [8:0] delayed_exp_out;

uvm_analysis_imp #(adder_tx, scoreboard) m_analysis_imp;

//Build phase: Initializes the analysis import port

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

m_analysis_imp = new("m_analysis_imp", this);

endfunction

/*write: Receives transactions, computes expected values,

and checks correctness*/

virtual function write(adder_tx item);

bit [8:0] expected_value = item.x + item.y;

exp_out_queue.push_back(expected_value);

if (exp_out_queue.size() > 1) begin

delayed_exp_out = exp_out_queue.pop_front();

`uvm_info("SCBD", $sformatf("x=%d y=%d out=%d

exp_out=%d", item.x, item.y, item.out, delayed_exp_out),

UVM_LOW)

if (item.out == delayed_exp_out) begin

`uvm_info("SCBD", $sformatf("PASS ! out=%0d,

exp=%0d", item.out, delayed_exp_out), UVM_LOW)

end else begin

`uvm_error("SCBD", $sformatf("ERROR ! out=%0d

exp=%0d", item.out, delayed_exp_out))

end

end

endfunction

endclass

```

### 3.2.7 Environment

This UVM environment (env) class is a key part of the testbench, serving as a container for the agent (a0) and scoreboard (sb0). The agent is responsible for driving and monitoring transactions, while the scoreboard checks if the DUT outputs are correct. The build\_phase() creates instances of the agent and scoreboard using the UVM factory. The connect\_phase() ensures that the monitor inside the agent (a0.m0) is connected to the scoreboard, allowing it to receive and compare transactions. This setup ensures that the verification environment collects data, compares results, and reports errors if the DUT's behavior does not match expectations.

```

import uvm_pkg::*;

`include "uvm_macros.svh"

import tb_pkg::*;

class env extends uvm env;

//Register this class with the UVM factory

`uvm_component_utils(env)

function new(string name = "env", uvm_component parent=null);

super.new(name, parent);

endfunction

agent a0;

scoreboard sb0;

//Build phase: Create instances of the agent and sb

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

a0 = agent::type_id::create("a0", this);

sb0 = scoreboard::type_id::create("sb0", this);

endfunction

//Connect phase: Connect the monitor's analysis port to the sb

virtual function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

a0.m0.mon_analysis_port.connect(sb0.m_analysis_imp);

endfunction

endclass

```

## 3.2.8 Test

This UVM testbench code defines a base test (base\_test) and a derived test (adder\_test) to verify an adder module. The base\_test class extends uvm\_test and serves as the foundation for all tests. It includes an environment (env e0), a sequence object (seq), and a virtual interface (vif) for interacting with the DUT.

The build\_phase() creates the test environment (e0), retrieves the adder interface (adder\_if) from the UVM configuration database, and randomizes the sequence (seq). If any of these steps fail, a fatal error is reported.

The run\_phase() raises an objection (preventing the test from ending immediately), calls apply\_reset() to reset the DUT, starts the sequence on the sequencer (e0.a0.s0), waits 200 time units, and then drops the objection, allowing the test to end.

The apply\_reset () task asserts reset, initializes input signals (x and y to 0), waits for five clock cycles, then deasserts reset, and waits for ten more clock cycles.

The adder\_test class extends base\_test and modifies the build\_phase() to ensure the sequence is randomized within a specific range (num between 300 and 500). If this randomization fails, the test reports a fatal error.

This testbench structure allows for reusable and automated verification of the adder module. The code can be seen in the following:

```

//Virtual interface to interact with the DUT

virtual adder_if vif;

/*Build phase: Initializes the environment,

gets the interface, and creates the sequence */

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

e0 = env::type id::create("e0", this);

if (!uvm_config_db#(virtual adder_if)::get(this, "",

"adder_vif", vif))

`uvm_fatal("TEST", "Did not get vif");

uvm_config_db#(virtual adder_if)::set(this, "e0.a0.*",

"adder_vif", vif);

seq = gen_item_seq::type_id::create("seq");

if (seq == null)

`uvm_fatal("TEST", "Sequence creation failed");

if (!seq.randomize())

`uvm_fatal("TEST", "Randomization failed for seq");

endfunction

//Run phase: Applies reset and runs the sequence

virtual task run_phase(uvm_phase phase);

phase.raise_objection(this);

apply_reset();

seq.start(e0.a0.s0);

#200;

phase.drop_objection(this);

endtask

//Apply reset sequence to the DUT

virtual task apply_reset();

vif.rst <= 1;</pre>

vif.x <= 0;

vif.y <= 0;

repeat(5) @ (posedge vif.clk);

vif.rst <= 0;

repeat(10) @ (posedge vif.clk);

endtask

endclass

//Derived test class that extends base_test

class adder_test extends base_test;

`uvm_component_utils(adder_test)

```

```

function new(string name="adder_test", uvm_component parent=null);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

if (!seq.randomize() with { num inside {[300:500]}; })

`uvm_fatal("TEST", "Randomization of seq.num failed!");

endfunction

endclass

```

#### 3.2.9 Testbench

This UVM testbench (tb) is designed to verify the functionality of an adder module using UVM methodology. The testbench first defines a clock signal and toggles it every 10 ns using an always block. The interface (adder\_if) is instantiated and connected to the DUT, which takes clk, rst, X, and Y as inputs and produces OUT as an output.

In the initial block, the clock is initialized to 0, and the virtual interface (\_if) is registered in the UVM configuration database using uvm\_config\_db::set(), allowing UVM testbench components (like the driver and monitor) to access it. The simulation starts by calling run\_test("adder\_test"), which triggers the execution of the UVM test. This setup ensures that the DUT operates in a controlled and reusable test environment, where the UVM framework handles stimulus generation, signal monitoring, and result checking.

```

timescale lns/lps

module tb;

import uvm_pkg::*;

include "uvm_macros.svh"

import tb_pkg::*;

reg clk;

always #10 clk = ~clk;

adder_if _if(clk);

```

# 3.2.10 Adder module

Basic Ripple Carry Adder used for test:

```

module adder(

input [7:0] X,

input [7:0] Y,

input clk,

input rst,

output reg [8:0] OUT

);

wire [7:0] w;

wire [8:0] OUT_tmp;

full_adder FA0(

.A(X[0]),

.B(Y[0]),

.Cin(1'b0),

.S(OUT_tmp[0]),

.Cout (w[0])

);

full_adder FA1(

.A(X[1]),

.B(Y[1]),

.Cin(w[0]),

.S(OUT_tmp[1]),

.Cout (w[1])

);

```

```

full_adder FA2(

.A(X[2]),

.B(Y[2]),

.Cin(w[1]),

.S(OUT_tmp[2]),

.Cout(w[2])

);

full_adder FA3(

.A(X[3]),

.B(Y[3]),

.Cin(w[2]),

.S(OUT_tmp[3]),

.Cout (w[3])

);

full_adder FA4(

.A(X[4]),

.B(Y[4]),

.Cin(w[3]),

.S(OUT_tmp[4]),

.Cout(w[4])

);

full_adder FA5(

.A(X[5]),

.B(Y[5]),

.Cin(w[4]),

.S(OUT_tmp[5]),

.Cout(w[5])

);

full_adder FA6(

.A(X[6]),

.B(Y[6]),

.Cin(w[5]),

.S(OUT_tmp[6]),

.Cout (w[6])

);

full_adder FA7(

.A(X[7]),

.B(Y[7]),

.Cin(w[6]),

.S(OUT_tmp[7]),

.Cout (w[7])

);

assign OUT_tmp[8] = w[7];

```

```

always @(posedge clk) begin

if(rst) OUT <= 8'b00000000;

else OUT <= OUT_tmp;

end

endmodule</pre>

```

Error putted in the last stage of full adder chain:

```

module adder(

input [7:0] X,

input [7:0] Y,

input clk,

input rst,

output reg [8:0] OUT

);

wire [7:0] w;

wire [8:0] OUT_tmp;

full_adder FA0(

.A(X[0]),

.B(Y[0]),

.Cin(1'b0),

.S(OUT_tmp[0]),

.Cout(w[0])

);

full_adder FA1(

.A(X[1]),

.B(Y[1]),

.Cin(w[0]),

.S(OUT_tmp[1]),

.Cout(w[1])

);

full_adder FA2(

.A(X[2]),

.B(Y[2]),

.Cin(w[1]),

.S(OUT_tmp[2]),

.Cout (w[2])

);

full_adder FA3(

.A(X[3]),

```

```

.B(Y[3]),

.Cin(w[2]),

.S(OUT_tmp[3]),

.Cout(w[3])

);

full_adder FA4(

.A(X[4]),

.B(Y[4]),

.Cin(w[3]),

.S(OUT_tmp[4]),

.Cout(w[4])

);

full_adder FA5(

.A(X[5]),

.B(Y[5]),

.Cin(w[4]),

.S(OUT_tmp[5]),

.Cout (w[5])

);

full_adder FA6(

.A(X[6]),

.B(Y[6]),

.Cin(w[5]),

.S(OUT_tmp[6]),

.Cout (w[6])

);

full_adder FA7(

.A(X[7]),

.B(Y[7]),

.Cin(1'b0),

.S(OUT_tmp[7]),

.Cout (w[7])

);

assign OUT_tmp[8] = w[7];

always @(posedge clk) begin

if(rst) OUT <= 8'b00000000;</pre>

else OUT <= OUT_tmp;</pre>

end

endmodule

```

## 3.3 UVM Factory

The UVM Factory is a centralized object creation mechanism in UVM. It allows testbench components such as drivers, monitors, agents, environments, and sequences to be dynamically created at runtime instead of being instantiated manually in the code. This makes the testbench more flexible and reusable, as different configurations can be applied without modifying the source code.

In the adder verification testbench, the factory is used to create various UVM components dynamically. For example, an agent, monitor, and driver are instantiated using the type\_id::create("instance\_name", parent) method. This ensures that these components are correctly registered with the UVM framework and can be overridden if needed.

Example usage in the adder testbench:

```

env e0;

e0 = env::type_id::create("e0", this);

```

This method ensures that the environment (env) can be replaced with different implementations if required, making the verification environment scalable and configurable.

#### 3.4 Basic UVM Macros Used in Adder Verification

UVM provides several macros to simplify testbench development. Below are some of the most basic macros used in the adder verification:

## 3.4.1 uvm\_component\_utils

This macro registers a UVM component with the factory so it can be created dynamically. It is required in every UVM component class.

Example from the agent:

```

class agent extends uvm_agent;

`uvm_component_utils(agent)

```

Without this macro, the factory cannot create instances of the agent class.

## 3.4.2 uvm\_object\_utils

Similar to uvm\_component\_utils, this macro registers UVM objects (such as sequence items) with the factory. Unlike components, sequence items (uvm\_sequence\_item) do not have a hierarchy.

Example from the sequence item:

```

class adder_tx extends uvm_sequence_item;

`uvm_object_utils(adder_tx)

```

This enables randomization and dynamic creation of transactions.

## 3.4.3 uvm\_fatal

This macro reports a fatal error and stops the simulation immediately if a critical issue occurs. It is used in cases where the testbench cannot proceed.

Example from the driver:

```

if (!uvm_config_db#(virtual adder_if)::get(this, "",

"adder_vif", vif))

`uvm_fatal("DRV", "Could not get vif");

```

If the virtual interface (vif) is not set up correctly, the testbench will halt with an error.

## 3.4.4 uvm\_info

This macro is used for logging informational messages during simulation. It helps in debugging by providing insights into the testbench operation.

Example from the monitor:

```

`uvm_info("MON", $sformatf("Saw item %s",

item.convert2str()), UVM_HIGH)

```

This logs transactions observed by the monitor, which helps in tracking the values sent to the DUT.

## 3.4.5 uvm\_error

This macro is used to report an error in the testbench but does not stop the simulation immediately like uvm\_fatal. It is useful for detecting incorrect DUT outputs while allowing further execution.

Example from the scoreboard:

```

if (item.out != delayed_exp_out)

`uvm_error("SCBD", $sformatf("ERROR ! out=%0d exp=%0d",

item.out, delayed_exp_out))

```

If the DUT output does not match the expected value, this error will be reported, but the test will continue running.

### 3.5 UVM Testbench Results

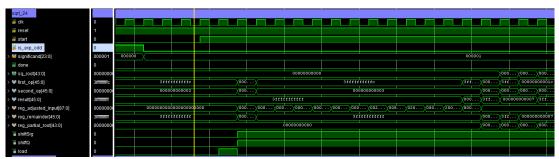

The UVM testbench starts with a text in the Figure 3.3.

Figure 3.3: UVM testbench start.

For the working adder module the PASS messages are in the Figure 3.4.

```

# UVM_INFO adder_scoreboard.sv(31) @ 330000: uvm_test_top.e0.sb0 [SCBD] x= 44 y=135 out= 94 exp_out= 94

# UVM_INFO adder_scoreboard.sv(34) @ 330000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=94, exp=94

# UVM_INFO adder_scoreboard.sv(31) @ 350000: uvm_test_top.e0.sb0 [SCBD] x=131 y=165 out=179 exp_out=179

# UVM_INFO adder_scoreboard.sv(34) @ 350000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=179, exp=179

# UVM_INFO adder_scoreboard.sv(31) @ 370000: uvm_test_top.e0.sb0 [SCBD] x=243 y=163 out=296 exp_out=296

# UVM_INFO adder_scoreboard.sv(34) @ 370000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=296, exp=296

# UVM_INFO adder_scoreboard.sv(31) @ 390000: uvm_test_top.e0.sb0 [SCBD] x=252 y=203 out=406 exp_out=406

# UVM_INFO adder_scoreboard.sv(34) @ 390000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=406, exp=406

# UVM_INFO adder_scoreboard.sv(31) @ 410000: uvm_test_top.e0.sb0 [SCBD] x= 74 y=180 out=455 exp_out=455

# UVM_INFO adder_scoreboard.sv(34) @ 410000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=455, exp=455

# UVM_INFO adder_scoreboard.sv(31) @ 430000: uvm_test_top.e0.sb0 [SCBD] x=108 y=123 out=254 exp_out=254

# UVM_INFO adder_scoreboard.sv(34) @ 430000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=254, exp=254

# UVM_INFO adder_scoreboard.sv(31) @ 450000: uvm_test_top.e0.sb0 [SCBD] x= 43 y= 15 out=231 exp_out=231

# UVM_INFO adder_scoreboard.sv(34) @ 450000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=231, exp=231

# UVM_INFO adder_scoreboard.sv(31) @ 470000: uvm_test_top.e0.sb0 [SCBD] x=155 y=190 out= 58 exp_out= 58

# UVM_INFO adder_scoreboard.sv(34) @ 470000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=58, exp=58

```

**Figure 3.4**: PASS messages coming from the scoreboard.

When the working adder module is given the results are in the Figure 3.5.

```

# --- UVM Report Summary ---

# ** Report counts by severity

# UVM_INFO: 881

# UVM_MARNING: 0

# UVM_FATAL: 0

# UVM_FATAL: 0

# ** Report counts by id

# [Questa UVM] 2

# [RNIST] 1

# [SCBD] 876

# [SESD] 1

# [TEST_DONE] 1

# ** Note: $finish : /sw/mentor/questasim/2019.4_1/questasim/linux_x86_64/../verilog_src/uvm-1.1d/src/base/uvm_root.svh(430)

# Time: 8850200 ps Iteration: 54 Instance: /tb

```

**Figure 3.5**: UVM report summary for the correct adder module.

When the incorrect adder module is given to the testbench the scoreboard shows errors like in the Figure 3.6.

```

# UVM_INFO adder_scoreboard.sv(31) @ 8570000: uvm_test_top.e0.sb0 [SCBD] x=249 y= 63 out=362 exp_out=362 # UVM_INFO adder_scoreboard.sv(34) @ 8570000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=362, exp=362 # UVM_INFO adder_scoreboard.sv(31) @ 8590000: uvm_test_top.e0.sb0 [SCBD] x= 12 y=170 out=184 exp_out=312 # UVM_ERROR adder_scoreboard.sv(36) @ 8590000: uvm_test_top.e0.sb0 [SCBD] ERROR ! out=184 exp=312 # UVM_INFO adder_scoreboard.sv(31) @ 8610000: uvm_test_top.e0.sb0 [SCBD] x= 88 y=192 out=182 exp_out=182 # UVM_INFO adder_scoreboard.sv(34) @ 8610000: uvm_test_top.e0.sb0 [SCBD] PASS ! out=182, exp=182

```

**Figure 3.6**: ERROR messages coming from the scoreboard.

The incorrect adder module's UVM report summary is in the Figure 3.7.

**Figure 3.7**: UVM report summary for the incorrect adder module.

#### 4. IBEX VERIFICATION ENVIRONMENT

## 4.1 Getting the Ibex Environment Running

### 4.1.1 Initial attempt

We start by setting up the verification environment according to Ibex's documentation [3]:

As described in the documentation, the following lines are added to the .bashrc file, to have them set automatically at system startup:

```

export PATH=$PATH:/opt/riscv/bin

export RISCV=/opt/riscv/

export RISCV_GCC=/opt/riscv/bin/riscv32-unknown-elf-gcc

export RISCV_TOOLCHAIN=$RISCV

export RISCV_OBJCOPY=/opt/riscv/bin/riscv32-unknown-elf-objcopy

export SPIKE_PATH_=/opt/riscv/bin/spike

export PKG_CONFIG_PATH=/opt/riscv/lib/pkgconfig

```

Then, as stated in the documentation, the command make was run from the directory ./ibex/dv/uvm/core\_ibex/. This makefile calls a Python script found in the directory ./ibex/dv/uvm/core\_ibex/scripts/.

Error messages were encountered, as the libraries used in this script weren't installed. Since the documentation did not provide a list of requirements, the missing libraries were installed one by one, until the error messages went away.

After installing all the required packages, the following error message appeared:

```

RuntimeError: Failed to find ['riscv-riscv', \\

'riscv-disasm', 'riscv-fdt', 'riscv-fesvr'] \\

pkg-config packages.

Did you set the PKG_CONFIG_PATH correctly?

```

After checking, it was found that this package wasn't installed in our system. Assuming this was a possible misconfiguration during the compilation of thee Spike ISA Simulator, it was recompiled with the commands:

```

./configure --prefix=$RISCV

make -j 12

```

This didn't alleviate the problem, as the required riscv-fdt.pc file was still missing. As a temporary fix, the requirement of this file was removed from the compile\_tb.py python script.

This led to the next error: No such file 'xrun'. This is the command to run Cadence's Xcelium simulator. As was described in the documentation, this environment requires a SystemVerilog simulator that supports UVM. These were listed in the Ibex documentation as Synopsys VCS, Cadence Xcelium and Questa. This requirement is the source of our technical problems.

## **4.1.2** Trying to obtain a working environment

Cadence Xcelium was available to use, via the Embedded Systems Design Lab's server. But, since the license was borrowed from the VLSI Lab, there were issues accessing the software. While the system administrators were trying to solve the problem, we decided to set up the other requirements on the server, namely the RISC-V Toolchain and Spike ISA Simulator.

The RISC-V Toolchain source code [10] was downloaded using git clone, and compiled with:

```

./configure --prefix=/opt/riscv --with-abi=ilp32f \\

--with-arch=rv32imf_zicsr_zicntr

make -j 12

```

This resulted in an error, since the user account assigned to us in the server did not have access to the folder /opt/riscv. To bypass this issue, we decided to install the toolchain to the user directory instead, by modifying the --prefix parameter. Compiling with these parameters resulted in several errors, caused by git commands. After checking, it was realized that the version of git used in the server, which is

running CentOS 7, is 11 years out of date. This version lacked the git submodule command the makefile used. This command allows the compilation to download the additional modules as needed. To not use this command, the repository can be cloned with git clone --recursive, which downloads all the required modules.

Even this isn't enough to solve the problem though, since the other tools in the server, mainly gcc, are also 11 years out of date. The RISC-V Toolchain is not compatible with build environments that are this old, so we were unable to obtain these tools on the server. Other methods, such as compiling the tools on our personal computers and copying them, or downloading other pre-compiled binaries were tested. Since these both depend on the host system to have up-to-date libraries, they too were unable to be run on the server.

Obtaining up-to-date compilation tools on the server might require a whole system upgrade, so it wasn't possible during the academic term. Another option is obtaining a Questa license from ElectraIC, the company aiding us with the project. That has also been delayed due to schedule issues, therefore we decided to focus on fixing Hornet instead.

## 4.2 Setting Up and Analyzing the Environment

By utilizing a server equipped with Questa Sim and RISC-V tools, access to which was provided by Electra IC, the Ibex Verification Environment was successfully run. Before doing so, however, making several changes to the configuration files were required. Before discussing the changes, it is beneficial to briefly mention the files most utilized within this chapter with Table 4.1.

## **4.2.1** Setup of the environment

In the current versions of the Ibex Verification Environment [3], the verification flow utilizes co-simulation, in which the ISS and RTL simulations are run synchronized with each other. Because of this reason, the core trace log based verification method, which we aim to utilize, is absent. For this reason, an older branch of the environment, modified to accept the Pulpissimo RISC-V core [11], will be utilized. This branch still contains all the trace log comparison structure required.

**Table 4.1**: File descriptions and their purposes.

| File                               | Purpose                                          |

|------------------------------------|--------------------------------------------------|

| Makefile                           | Defines ISA, ABI, simulation flow, and           |

|                                    | toolchain parameters                             |

| rtl_simulation.yaml                | Command line parameters for various RTL          |

|                                    | simulators used to simulate the core under test. |

|                                    | These parameters control simulation behavior     |

|                                    | and debugging options.                           |

| simulator.yaml                     | Configuration used by RISCV-DV [4] to            |

|                                    | compile the instruction generator and generate   |

|                                    | random instructions. Similar to but separate     |

|                                    | <pre>from rtl_simulation.yaml.</pre>             |

| testlist.yaml                      | Comprehensive list of tests and their gener-     |

|                                    | ation parameters, including test weights and     |

|                                    | constraints.                                     |

| riscv_core_setting.sv              | SystemVerilog file defining core capabilities    |

|                                    | including supported ISA extensions and reg-      |

|                                    | ister count.                                     |

| <pre>ibex_asm_program_gen.sv</pre> | Generates assembly program headers includ-       |

|                                    | ing various directives like .option flags and    |

|                                    | memory initialization sequences.                 |

| core_ibex_tb_top.sv                | Top-level testbench module that instantiates     |

|                                    | and connects the DUT (Design Under Test)         |

|                                    | with all test interfaces and verification compo- |

|                                    | nents.                                           |

| ibex_dv.f                          | Simulation file list for Questa simulator,       |

|                                    | containing all required design and verification  |

|                                    | files.                                           |

To get this environment working with the Questa sim, several fixes to the aforementioned files are required. These are:

- In ibex/dv/uvm/core\_ibex/Makefile, changing the ISA parameter from rv32imcb to rv32imc

- In ibex/dv/uvm/core\_ibex/yaml/rtl\_simulation.yaml, adding several parameters to Questa launch options, to point to the UVM source files. To be specific, changing line 76 from

```

vsim -64 -c <cov_opts> -do "run -a; quit -f" +designfile

-f <out>/top.list <sim_opts> -sv_seed <seed> +access +r+w

+UVM_TESTNAME=<rtl_test> +bin=<binary>

```

```

+ibex_tracer_file_base="<sim_dir>/trace_core"

-l <sim_dir>/sim.log

```

to

```

vsim -64 -c <cov_opts> -t 1ps -sv_lib

$UVM_HOME/linux_x86_64/uvm_dpi -L \$UVM_HOME

-dpicpppath /usr/bin/gcc -do "run -a; quit -f"

+designfile -f <out>/top.list <sim_opts> -sv_seed <seed>

+access +r+w +UVM_TESTNAME=<rtl_test> +bin=<binary>

+ibex_tracer_file\base="<sim_dir>/trace_core"

-l <sim_dir>/sim.log

```

- Similar additions to above were also done in ibex/vendor/google\_riscv-dv/yaml/simulator.yaml.

- In ibex/rtl/ibex\_core.sv, instantiating the prim\_clock\_gating module instead of the tc\_clk\_gating.

- Finally, in

```

ibex/vendor/google_riscv-dv/scripts/spike_log_to_trace_csv.py

```

, the regex for parsing the log into a csv file was malformed, requiring a fix. Doing this by hand would be complicated, but the fix was already available on the master branch of the github repo, so it was pulled from there.

After applying these fixes, and running the environment with

```

make TEST=riscv_rand_instr_test ITERATIONS=1

```

, the test is successfully completed as it can be seen in 4.1

```

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Found matched tests: riscv_rand_instr_test. Freations: 1

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat, 65 Apr 2025 14:52:43 INFO

Sat,

```

Figure 4.1: Terminal output for successful Ibex Verification.