# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

## REALIZATION OF FREQUENCY BASED IMAGE STEGANOGRAPHY USING RISC-V PROCESSOR

# **SENIOR DESIGN PROJECT**

Yaşar Utku ALÇALAR Sinem Başak KAPUCU Burcu TÜRK

ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

## REALIZATION OF FREQUENCY BASED IMAGE STEGANOGRAPHY USING RISC-V PROCESSOR

## **SENIOR DESIGN PROJECT**

Yaşar Utku ALÇALAR 040170054

Sinem Başak KAPUCU 040180005

> Burcu TÜRK 040170052

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

Project Advisor: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> <u>ELEKTRİK-ELEKTRONİK FAKÜLTESİ</u>

# FREKANS TEMELLİ GÖRÜNTÜ STEGANOGRAFİSİNİN RISC-V İŞLEMCİ KULLANILARAK GERÇEKLENMESİ

## LİSANS BİTİRME TASARIM PROJESİ

Yaşar Utku ALÇALAR 040170054

Sinem Başak KAPUCU 040180005

> Burcu TÜRK 040170052

Proje Danışmanı: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

ELEKTRONİK VE HABERLEŞME MÜHENDİSLİĞİ BÖLÜMÜ HAZİRAN, 2022

We are submitting the Senior Design Project Report entitled as "REALIZATION OF FREQUENCY BASED IMAGE STEGANOGRAPHY USING RISC-V PROCESSOR". The Senior Design Project Report has been prepared as to fulfill the relevant regulations of the Electronics and Communication Engineering Department of Istanbul Technical University. We hereby confirm that we have realized all stages of the Senior Design Project work by ourselves and we have abided by the ethical rules with respect to academic and professional integrity .

Yaşar Utku ALÇALAR 040170054

Sinem Başak KAPUCU 040180005

**Burcu TÜRK** 040170052

To our loved ones,

### **FOREWORD**

We would like to express our gratitude to our project advisor Prof. Dr. Sıddıka Berna Örs Yalçın who helped us throughout the process and guided us through the exciting world of digital electronics and cryptography. We are also thankful for our university faculty for encouraging us in the way of becoming successful engineers.

Finally, we would like to thank deeply to our families who supported our education and helped us become who we are.

June 2022

Yaşar Utku ALÇALAR Sinem Başak KAPUCU Burcu TÜRK

# TABLE OF CONTENTS

|                                                                           | Page  |

|---------------------------------------------------------------------------|-------|

| FOREWORD                                                                  | xi    |

| TABLE OF CONTENTS                                                         |       |

| ABBREVIATIONS                                                             | XV    |

| SYMBOLS                                                                   | .xvii |

| LIST OF TABLES                                                            | xix   |

| LIST OF FIGURES                                                           | xxi   |

| SUMMARY                                                                   | xxiii |

| ÖZET                                                                      | . xxv |

| 1. INTRODUCTION                                                           | 29    |

| 1.1 Purpose of Project                                                    | 29    |

| 1.2 Literature Review                                                     | 29    |

| 1.2.1 Image steganography                                                 | 29    |

| 1.2.2 LFSR                                                                | 30    |

| 1.2.3 Frequency based algorithms                                          |       |

| 2. BASIC INFORMATION AND CONCEPTS                                         | 31    |

| 2.1 Cryptography                                                          |       |

| 2.2 Image Steganography                                                   | 32    |

| 2.3 RISC-V Processor                                                      | 34    |

| 2.4 Xilinx Vivado Environment                                             | 35    |

| 3. ALGORITHMS                                                             | 37    |

| 3.1 LSB Algorithm                                                         |       |

| 3.2 LFSR Algorithm                                                        |       |

| 3.2.1 Motivation for using the LFSR algorithm                             | 38    |

| 3.2.2 Mathematics behind the LFSR algorithm                               |       |

| 3.3 Frequency Detection Based Algorithm                                   |       |

| 3.3.1 Motivation for using a frequency detection based algorithm          |       |

| 3.3.2 Mathematics behind the selected frequency detection based algorithm |       |

| 3.4 MATLAB Simulation of the Algorithms                                   |       |

| 3.4.1 LSB based image steganography                                       |       |

| 3.4.2 Including LFSR into the algorithm                                   |       |

| 3.4.3 Improving the algorithm with frequency detection                    |       |

| 4. IBEX CORE AND WISHBONE PROTOCOL                                        |       |

| 4.1 Preparing the Work Environment                                        |       |

| 4.1.1 Installing Linux operating system                                   |       |

| 4.1.2 Installing Vivado Design Suite for Linux OS                         |       |

| 4.1.3 Installing RISC-V GNU toolchain                                     |       |

| 4.2 Implementation of Ibex Core                                           |       |

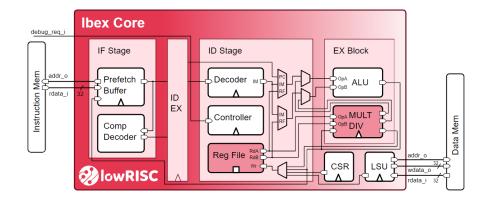

| 4.2.1 Ibex core overview                                                  |       |

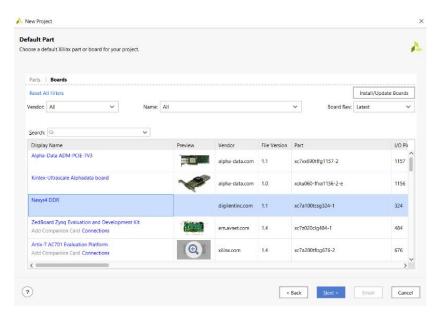

| 4.2.2 Creating a Vivado project                                           |       |

| 4.2.3 RAM initialization                                                  |       |

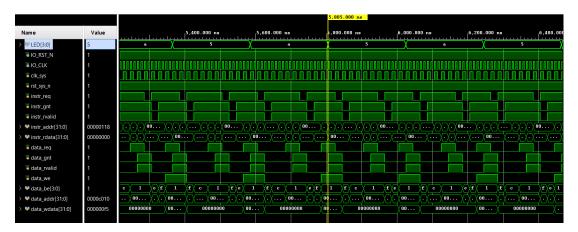

| 4.2.4 Vivado simulation                                                   |       |

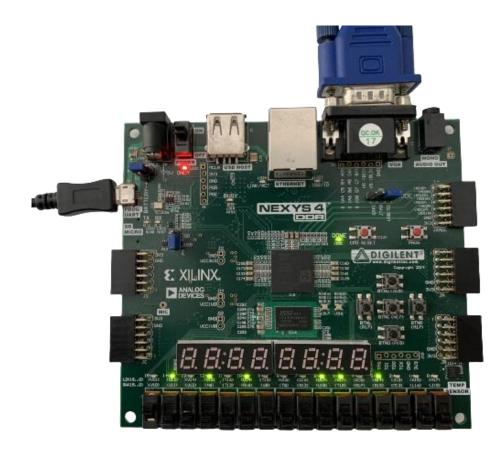

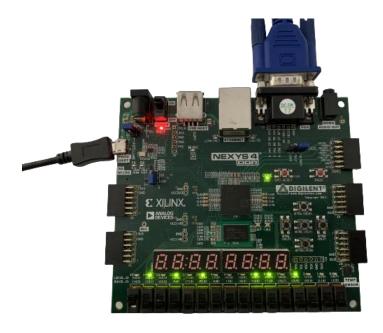

| 4.2.5 Implementation on the FPGA                                          | 56    |

| 4.3 Integrating Wishbone Protocol with Ibex Core                        | 57  |

|-------------------------------------------------------------------------|-----|

| 4.3.1 Wishbone protocol                                                 |     |

| 4.3.2 Adding an Ibex core into the Wishbone and existing peripherals    | 58  |

| 5. FPGA IMPLEMENTATION                                                  |     |

| 5.1 Iplementation of Image Steganography with LSB                       | 61  |

| 5.1.1 C code generation for programming Ibex                            | 61  |

| 5.1.2 Simulation results on Vivado                                      | 65  |

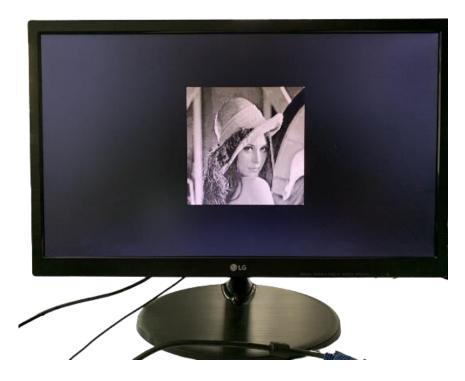

| 5.1.3 Physical visualization of the implementation                      | 67  |

| 5.2 Iplementation of Image Steganography with LSB Using LFSR Algorithm  | 71  |

| 5.2.1 C code generation for programming Ibex                            | 71  |

| 5.2.2 Simulation results on Vivado                                      | 74  |

| 5.2.3 Physical visualization of the implementation                      | 76  |

| 5.3 Iplementation of Image Steganography with Frequency Based Algorithm | 78  |

| 5.3.1 C code generation for programming Ibex                            | 78  |

| 5.3.2 Simulation results on Vivado                                      |     |

| 5.3.3 Physical visualization of the implementation                      | 83  |

| 5.4 Improving the Frequency Based Algorithm With Two Thresholds         | 86  |

| 5.4.1 Modifying the C code for programming Ibex                         | 86  |

| 5.4.2 Simulations for the algorithm                                     |     |

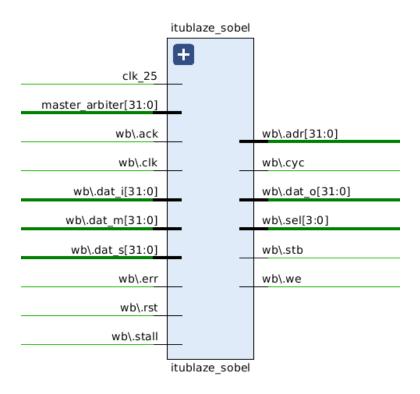

| 5.5 Custom IP Design for Frequency Detection                            | 89  |

| 5.5.1 Custom IP architecture in Vivado                                  |     |

| 5.5.2 Visualization of the filtered image using a custom IP             |     |

| 6. REALISTIC CONSTRAINTS AND CONCLUSIONS                                | 95  |

| 6.1 Practical Application of this Project                               |     |

| 6.2 Realistic Constraints                                               |     |

| 6.2.1 Social, environmental and economic impact                         | 95  |

| 6.2.2 Cost analysis                                                     | 95  |

| 6.2.3 Standards                                                         | 96  |

| 6.2.4 Health and safety concerns                                        | 96  |

| 6.3 Future Work and Recommendations                                     | 96  |

| REFERENCES                                                              | 97  |

| APPENDICES                                                              | 99  |

| APPENDIX A                                                              | 100 |

| APPENDIX B                                                              | 105 |

| APPENDIX C                                                              | 107 |

| APPENDIX D                                                              | 108 |

| CURRICULUM VITAE                                                        | 113 |

#### **ABBREVIATIONS**

**2D** : Two-dimensional

**ASCII** : American Standard Code for Information Interchange

**FPGA** : Field Programmable Gate Array

**GNU** : GNU's Not Unix

HDL : Hardware Definition Language

**IEEE** : The Institute of Electrical and Electronics Engineers

IP : Intellectual Property

: Instruction Set Architecture **ISA**

LED : Light-Emitting Diode

LFSR : Linear Feedback Shift Register Linux : Lovable Intellect Not Using XP

**LSB** : Least Significant Bit **LTS** : Long-Term Support **MATLAB** : Matrix Laboratory OS : Operating System

**RAM** : Random Access Memory

**RISC** : Reduced Instruction Set Computer

**ROM** : Read-Only Memory

**RSA** : Rivest–Shamir–Adleman **RTL**

: Register-Transfer Level

SoC : System on Chip

SRAM : Static Random Access Memory

# **SYMBOLS**

\$ : Ubuntu Terminal Command

$G_x$ : Gradient in x-direction

$G_y$ : Gradient in y-direction

# LIST OF TABLES

|                                                             | Page |

|-------------------------------------------------------------|------|

| Table 2.1 : Table with RISC-V examples.                     | 34   |

| Table 5.1 : Encoding process for first 8 bits of the image. |      |

# LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>Page</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

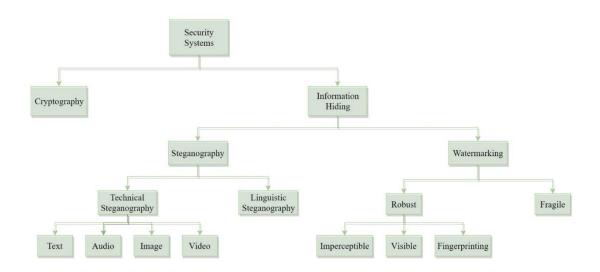

| Figure 2.1: Types of security systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32          |

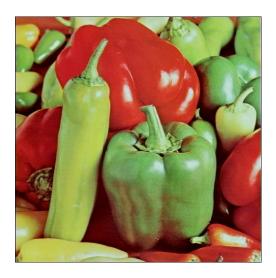

| Figure 2.2: Peppers cover image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

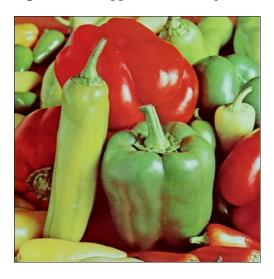

| Figure 2.3: Peppers stego-image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

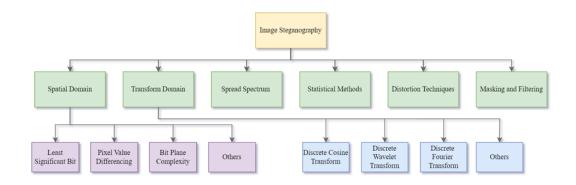

| Figure 2.4: Image steganography techniques and method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

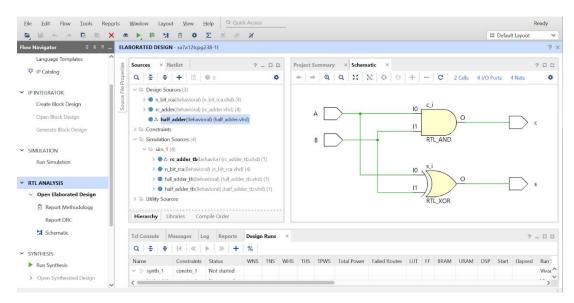

| Figure 2.5 : Xilinx Vivado environment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

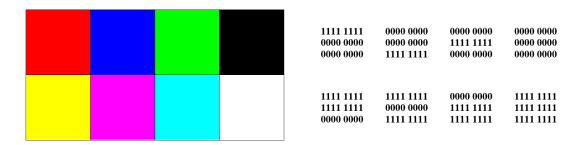

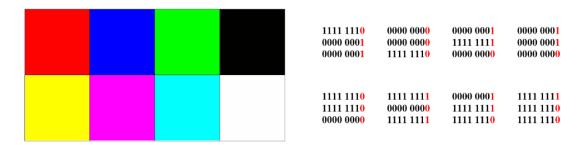

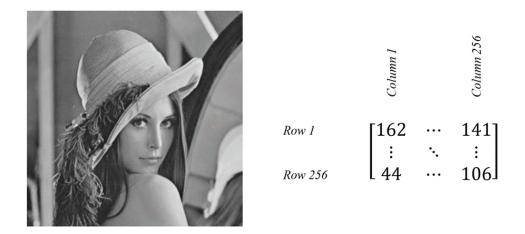

| Figure 3.1: Cover image and its binary values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37          |

| Figure 3.2: Message in binary form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| Figure 3.3: Stego-image and its binary values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38          |

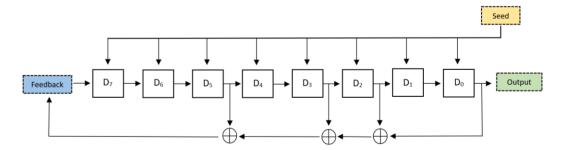

| <b>Figure 3.4 :</b> Representation of LFSR algorithm using $p(x) = x^8 + x^6 + x^5 + x^3 + x^3 + x^4 + x^4 + x^5 + x^4 + x^4 + x^4 + x^5 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4 + x^4$ | 140         |

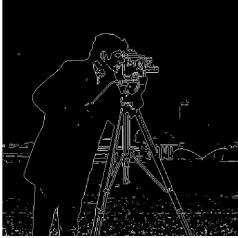

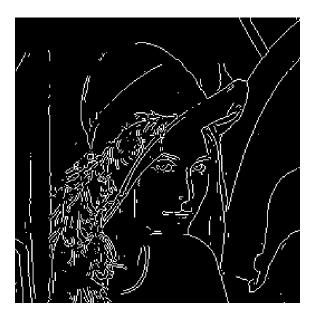

| Figure 3.5: Grayscale image and its gradient magnitude from Sobel operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

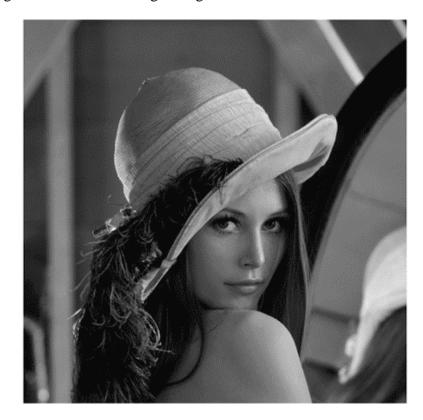

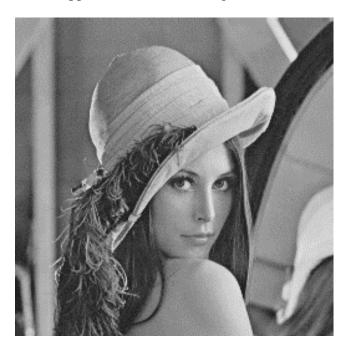

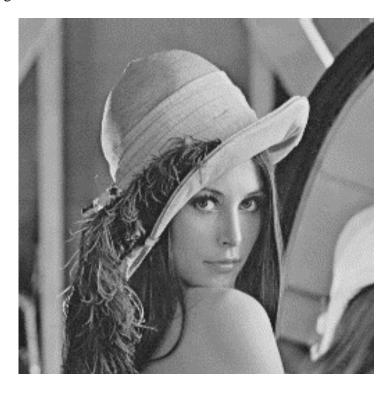

| Figure 3.6: Lena original image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43          |

| Figure 3.7: Lena stego-image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43          |

| Figure 3.8: MATLAB code for LFSR algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45          |

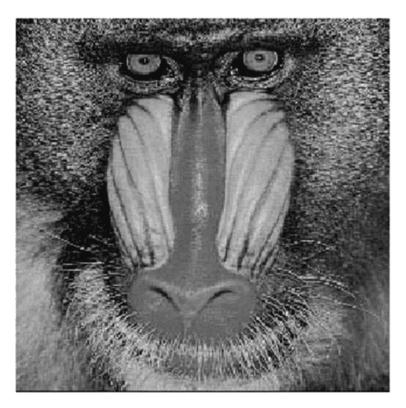

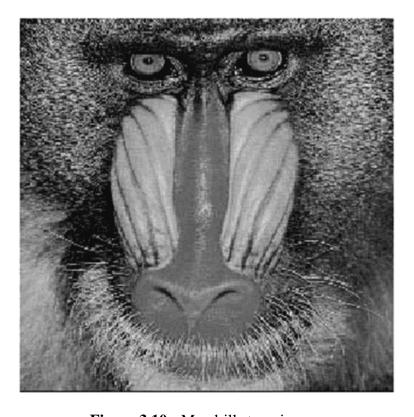

| Figure 3.9: Mandrill original image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46          |

| Figure 3.10 : Mandrill stego-image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| Figure 3.11: Gradient magnitude of the cover image from Sobel operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47          |

| Figure 3.12: MATLAB code for embedding process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48          |

| Figure 3.13: Lena original image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| Figure 3.14: Lena stego-image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49          |

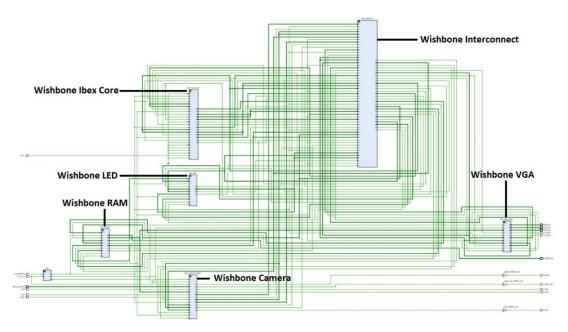

| Figure 4.1: Block diagram for Ibex core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| Figure 4.2: Board selection for the project.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

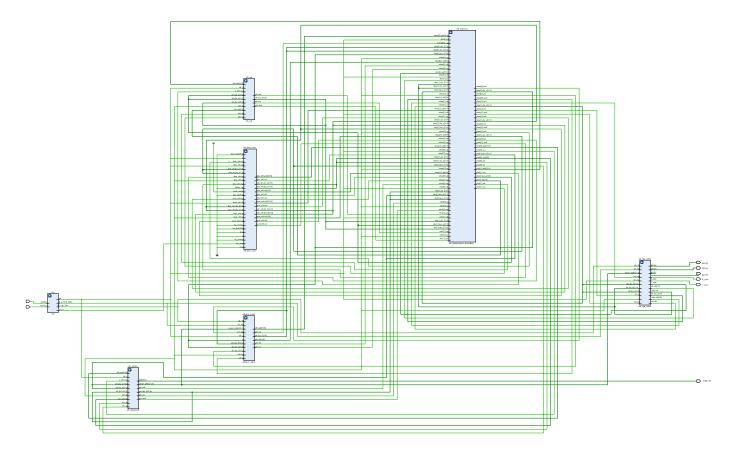

| <b>Figure 4.3 :</b> Hierarchy of the Ibex core project.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| <b>Figure 4.4 :</b> Compiled C code for the Ibex core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| <b>Figure 4.5 :</b> Terminal output after the compile operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| Figure 4.6: Timing diagram results in Vivado                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

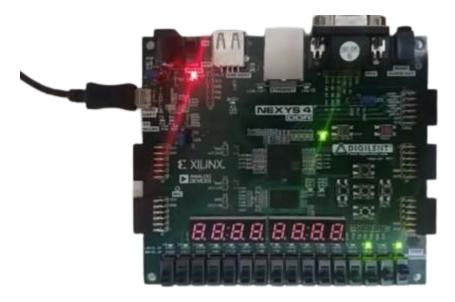

| <b>Figure 4.7 :</b> 0x5 value on the LEDs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

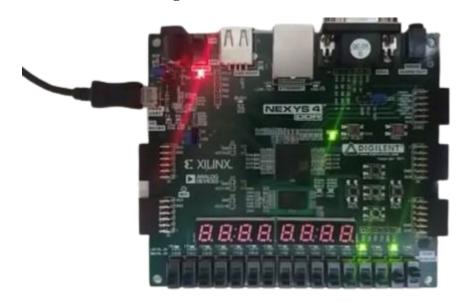

| Figure 4.8: 0xa value on the LEDs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

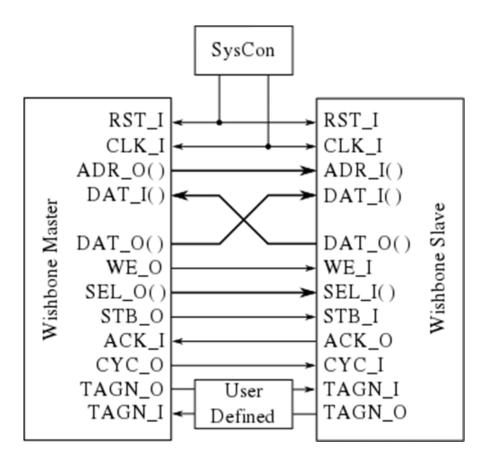

| Figure 4.9: Master and slave Wishbone's interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

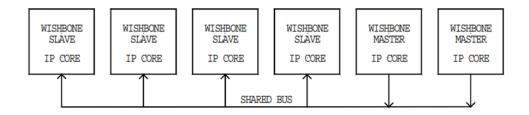

| Figure 4.10 : Shared bus interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

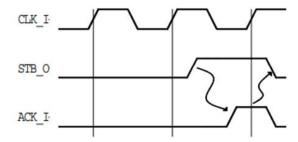

| Figure 4.11: Local bus handshaking protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

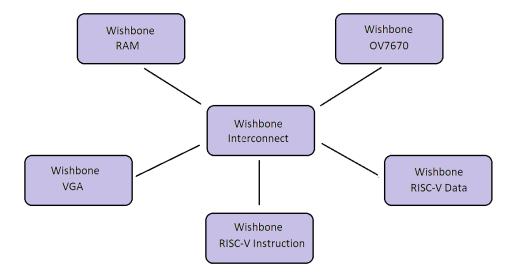

| Figure 4.12 : Interconnect management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |