# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

# VERIFICATION OF A SERIAL PERIPHERAL INTERFACE INTELLECTUAL PROPERTY BY USING UNIVERSAL VERIFICATION METHODOLOGY

**SENIOR DESIGN PROJECT**

**Berkay TURGAY**

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

FEBRUARY 2021

# ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

# VERIFICATION OF A SERIAL PERIPHERAL INTERFACE INTELLECTUAL PROPERTY BY USING UNIVERSAL VERIFICATION METHODOLOGY

# SENIOR DESIGN PROJECT

Berkay TURGAY 040150097

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

Project Advisor: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

FEBRUARY 2021

# İSTANBUL TEKNİK ÜNİVERSİTESİ ELEKTRİK-ELEKTRONİK FAKÜLTESİ

# BİR SERİ ÇEVRESEL ARAYÜZ FİKRİ MÜLKİYETİNİN EVRENSEL DOĞRULAMA METHODU İLE DOĞRULANMASI

LİSANS BİTİRME TASARIM PROJESİ

Berkay TURGAY 040150097

Proje Danışmanı: Prof. Dr. Sıddıka Berna ÖRS YALÇIN

ELEKTRONİK VE HABERLEŞME MÜHENDİSLİĞİ BÖLÜMÜ

ŞUBAT, 2021

We are submitting the Senior Design Project Report entitled as "VERIFICATION OF A SERIAL PERIPHERAL INTERFACE INTELLECTUAL PROPERTY BY USING UNIVERSAL VERIFICATION METHODOLOGY". The Senior Design Project Report has been prepared as to fulfill the relevant regulations of the Electronics and Communication Engineering Department of Istanbul Technical University. We hereby confirm that we have realized all stages of the Senior Design Project work by ourselves and we have abided by the ethical rules with respect to academic and professional integrity.

#### **Berkay TURGAY**

.....

040150097

### FOREWORD

I would like to thank to my mentor Prof. Dr. Sıddıka Berna Örs Yalçın who helped me to find this project and who allowed me to collaborate with ANKASYS and guided me throughout this project. Secondly, I would like to offer my gratitude to my other mentor Ekrem Şahin from ANKASYS who guided me in all of my mistakes and who helped me finish this project successfully. Without them, I would not finish this project properly. Finally, I would like to thank to my family and friends who supported me my entire life.

February 2021

Berkay TURGAY

## **TABLE OF CONTENTS**

| FOREWORD                                            | v    |

|-----------------------------------------------------|------|

| TABLE OF CONTENTS                                   | vii  |

| ABBREVIATIONS                                       | ix   |

| LIST OF FIGURES                                     | X    |

| SUMMARY                                             | xiii |

| ÖZET                                                |      |

| 1. INTRODUCTION                                     | 1    |

| 2. BACKGROUND INFORMATION                           | 2    |

| 2.1 Verification                                    |      |

| 2.2 Universal Verification Methodology              | 2    |

| 2.2.1 Verification Environment                      |      |

| 2.2.2 UVM Classes                                   | 4    |

| 2.2.3 UVM Phases                                    | 5    |

| 2.2.4 Transaction Level Modeling                    | 6    |

| 2.2.5 Top Block and Interface                       | 7    |

| 2.2.6 Components                                    | 8    |

| 2.2.6.1 Transaction                                 |      |

| 2.2.6.2 Sequence and Sequencer                      | 9    |

| 2.2.6.3 Driver                                      | 10   |

| 2.2.6.4 Monitor                                     | 11   |

| 2.2.6.5 Agent                                       | 12   |

| 2.2.6.6 Environment                                 | 13   |

| 2.2.6.7 Subscriber                                  | 14   |

| 2.2.6.8 Scoreboard                                  | 14   |

| 2.2.6.9 Test                                        | 16   |

| 2.3 Serial Peripheral Interface                     |      |

| 3. VERIFICATION AND SIMULATION TOOLS                |      |

| 3.1 Design Verification Kit                         | 22   |

| 3.2 QuestaSim                                       |      |

| 4.SERIAL PERIPHERAL INTERFACE INTELLECTUAL PROPERTY | 24   |

| 4.1 SPI Clock Generation                            |      |

| 4.2 Parallel Write Interface                        |      |

| 4.3 Parallel Read Interface                         | 26   |

| 5. VERIFICATION OF SERIAL PERIPHERAL INTERFACE      |      |

| INTELLECTUAL PROPERTY BY USING                      |      |

| UNIVERSAL VERIFICATION METHODOLOGY                  |      |

| 5.1 Top Block and Interface                         |      |

| 5.2 Transaction                                     |      |

| 5.3 Sequence and Sequencer                          | 30   |

| 5.4 Driver                                          | 32   |

| 5.5 Monitor                                         |      |

| 5.6 Agent                                           |      |

| 5.7 Environment                                     |      |

| 5.8 Subscriber                                      |      |

| 5.9 Config                                          | 48   |

| 5.10 Test                                       |    |

|-------------------------------------------------|----|

| 5.11 Simulation and Test Results                |    |

| 6. REALISTIC CONSTRAINTS AND CONCLUSIONS        | 63 |

| 6.1 Practical Application of this Project       |    |

| 6.2 Realistic Constraints                       |    |

| 6.2.1 Social, environmental and economic impact | 64 |

| 6.2.2 Cost analysis                             | 64 |

| 6.2.3 Standards                                 | 64 |

| 6.2.4 Health and safety concerns                | 64 |

| 6.3 Future Work and Recommendations             |    |

| REFERENCES                                      | 65 |

| CURRICULUM VITAE                                | 69 |

|                                                 |    |

# **ABBREVIATIONS**

| UVM   | : Universal Verification Methodology          |  |

|-------|-----------------------------------------------|--|

| SPI   | : Serial Peripheral Interface                 |  |

| DUT   | : Device Under Test                           |  |

| HDL   | : Hardware Description Language               |  |

| OVM   | : Open Verification Methodology               |  |

| I2C   | : Inter-Integrated Circuit                    |  |

| UART  | : Universal Asynchronous Receiver Transmitter |  |

| FSM   | : Finite State Machine                        |  |

| FPGA  | : Field Programmable Gate Array               |  |

| RAM   | : Random Access Memory                        |  |

| DVKit | : Design Verification Kit                     |  |

| IDE   | : Integrated Development Environment          |  |

| IP    | : Intellectual Property                       |  |

| VIP   | : Verification Intellectual Property          |  |

# LIST OF FIGURES

| Figure 2.1 : UVM Testbench Structure                                          |    |

|-------------------------------------------------------------------------------|----|

| Figure 2.2 : UVM Class Tree                                                   |    |

| Figure 2.3 : UVM Phases                                                       |    |

| Figure 2.4 : Transaction transfer via TLM ports                               |    |

| Figure 2.5 : Connection between testbench and the DUT via interface           | 7  |

| Figure 2.6 : Transaction Transfer Scheme                                      |    |

| Figure 2.7 : Sequence-driver communication via sequencer                      |    |

| Figure 2.8 : Transaction transfer from sequence to driver                     |    |

| Figure 2.9 : Transaction transfer from driver to DUT                          |    |

| Figure 2.10 : Monitor in a testbench                                          |    |

| Figure 2.11 : Agent class                                                     |    |

| Figure 2.12 : Environment class                                               |    |

| Figure 2.13 : Scoreboard's connections                                        |    |

| Figure 2.14 : Test class                                                      |    |

| Figure 2.15 : SPI Mode 0, CPOL=0, CPHA=0, CLK idle state=low                  |    |

| Figure 2.16 : SPI Mode 1, CPOL=0, CPHA=1, CLK idle state=low                  | 18 |

| Figure 2.17 : SPI Mode 2, CPOL=1, CPHA=0, CLK idle state=high                 | 18 |

| Figure 2.18 : SPI Mode 3, CPOL=1, CPHA=1, CLK idle state=high                 | 18 |

| Figure 2.19 : SPI diagram with all modes                                      | 19 |

| Figure 2.20 : Regular SPI mode structure                                      | 19 |

| Figure 2.21 : Daisy-chain mode                                                | 20 |

| Figure 3.1 : DVKit interface.                                                 | 22 |

| Figure 3.2 : QuestaSim interface                                              | 23 |

| Figure 4.1 : Parallel write sequence                                          | 25 |

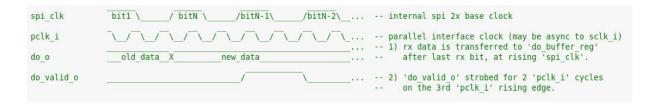

| Figure 4.2 : Parallel read sequence.                                          | 26 |

| Figure 5.1 : Interface.                                                       |    |

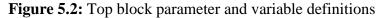

| Figure 5.2 : Top block parameter and variable definitions                     | 27 |

| Figure 5.3 : Top block adaptation layer and assertion instantiations          | 28 |

| Figure 5.4 : Top block adaptation layer and assetion instantiations continued |    |

| Figure 5.5 : Transaction.                                                     | 29 |

| Figure 5.6 : Slave sequence class constructor.                                | 30 |

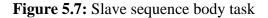

| Figure 5.7 : Slave sequence body task.                                        | 30 |

| Figure 5.8 : Master sequence                                                  | 31 |

| Figure 5.9: Master driver class constructor and build phase                   |    |

| Figure 5.10 : Master driver driverOff and driver Clk functions.               | 33 |

| Figure 5.11 : Master driver run phase.                                        | 33 |

| Figure 5.12 : Master driver run phase continued.                              |    |

| Figure 5.13 : Master driver SPI mode 0                                        | 34 |

| Figure 5.14: Master driver SPI mode 1                                         |    |

| Figure 5.15: Master driver SPI mode 2.                                        |    |

| Figure 5.16: Master driver SPI mode 3                                         | 36 |

| Figure 5.17 : Slave driver class constructor and build phase                  |    |

| Figure 5.18 : Slave driver run phase.                                         |    |

| Figure 5.19 : Slave driver SPI mode 0 and 1.                                  |    |

| Figure 5.20 : Slave driver SPI mode 2 and 3.                                  |    |

| -                                                                             |    |

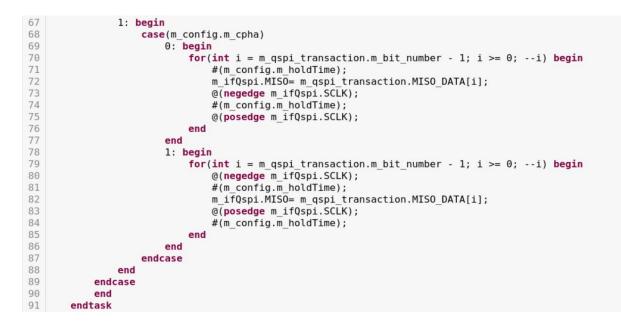

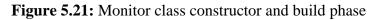

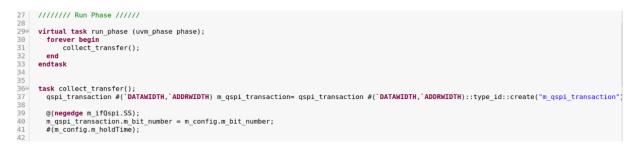

| <b>Figure 5.21 :</b> | Monitor class constructor and build phase         | 40 |

|----------------------|---------------------------------------------------|----|

| <b>Figure 5.22 :</b> | Monitor run phase and collect_transfer function   | 40 |

|                      | Monitor SPI mode 0 and 1.                         |    |

| <b>Figure 5.24 :</b> | Monitor SPI mode 2 and 3.                         | 41 |

|                      | Master agent class constructor and declarations.  |    |

|                      | Master agent build phase                          |    |

|                      | Master agent connect phase                        |    |

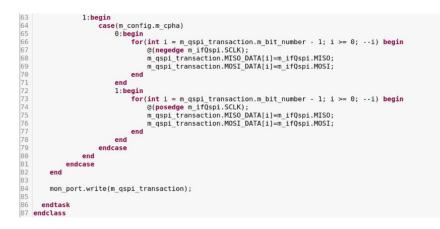

|                      | Slave agent class constructor and declarations    |    |

|                      | Slave agent build phase.                          |    |

|                      | Slave agent connect phase.                        |    |

|                      | Environment connections.                          |    |

|                      | Subsciber write_master function.                  |    |

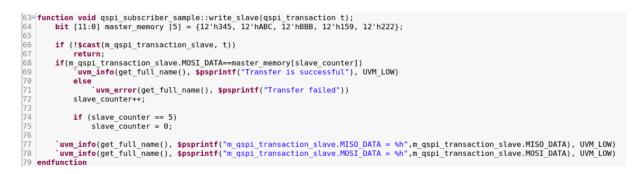

|                      | Subscriber write_slave function.                  |    |

| Figure 5.34 :        | Config class.                                     | 48 |

|                      | Config class continued.                           |    |

| •                    | Test class constructor and build phase.           |    |

| •                    | Test first sequence.                              |    |

| 0                    | Test second sequence.                             |    |

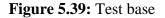

|                      | Test base                                         |    |

|                      | Design loopback                                   |    |

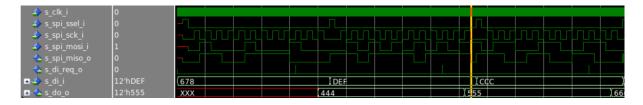

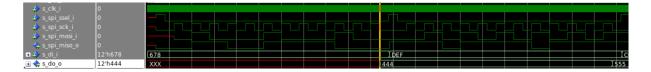

| 0                    | SPI mode 0, design=master testbench=slave.        |    |

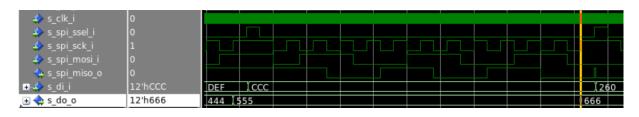

|                      | SPI mode 0, design=slave testbench=master.        |    |

|                      | SPI mode 0, design=master testbench=slave results |    |

|                      | SPI mode 0, design=slave testbench=master results |    |

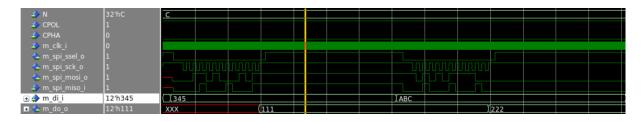

| 0                    | SPI mode 1, design=master testbench=slave.        |    |

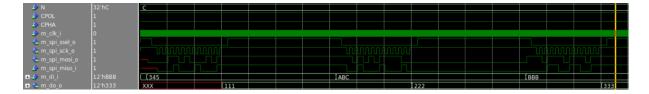

| •                    | SPI mode 1, design=slave testbench=master.        |    |

|                      | SPI mode 1, design=master testbench=slave results |    |

|                      | SPI mode 1, design=slave testbench=master results |    |

|                      | SPI mode 2, design=master testbench=slave.        |    |

|                      | SPI mode 2, design=slave testbench=master.        |    |

|                      | SPI mode 2, design=master testbench=slave results |    |

|                      | SPI mode 2, design=slave testbench=master results |    |

|                      | SPI mode 3, design=master testbench=slave.        |    |

|                      | SPI mode 3, design=slave testbench=master.        |    |

|                      | SPI mode 3, design=master testbench=slave results |    |

| Figure 5.56 :        | SPI mode 3, design=slave testbench=master results | 62 |

|                      |                                                   |    |

## VERIFICATION OF A SERIAL PERIPHERAL INTERFACE INTELLECTUAL PROPERTY BY USING UNIVERSAL VERIFICATION METHODOLOGY

#### SUMMARY

Due to increasing complexity of designed electronic systems, electronic system design industry is trying to handle the challenges of marketing time and the quality of the design. It is common to choose one over the other, but this compromise can be avoided. Focusing on "verifying correctly" can increase both productivity and quality. From an Intellectual Property (IP) to a System on Chip (SoC), successful design of any system depends on the correct verification. From chip level to card level and finally to system level, the cost of detecting an incorrect chip increases 10 times with each level pass. Sometimes, deciding a correct verification methodology is not easy, and choosing the wrong one can cause problems later. Verification IP (VIP) provides tools to make the correct assumption.

VIP is nothing but a model that provides a user interaction tool at different levels of abstraction of the basic design. Choosing the correct VIP, which includes identification and verification methodology, is as difficult as choosing a design IP. Correct methodology increases reusability. Debugging and error correcting is simple with the correct methodology. It also improves the ability to abstract the underlying complexity. Understanding how to build a permanent VIP is a challenge due to changing technologies and market conditions.

Serial Peripheral Interface (SPI) is a synchronous serial communication interface. SPI devices communicate in full duplex mode using a master-slave structure. The data from the master or the slave is adjusted on the rising or falling edge of the clock. Master and slave can send data simultaneously. Data is transferred between the master and the slave and that transfer is synchronized to the clock that is created by the master. SPI has 4 signals. These are Clock(SCLK,CLK), chip select/slave select(CS,SS), master-in slave-out(MISO) and master-out slave-in(MOSI). MOSI and MISO are the data lines. Throughout the communication, the data is synchronously sent and acquired via MOSI and MISO lines, since SPI is a full-duplex interface. In SPI, one master can communicate with multiple slaves. Master can select the specific slave to send data or receive data from, by using the Slave Select (SS) signal.

In this project, an SPI Master-Slave Interface design will be used. For the verification of this design, a VIP will be created by using UVM and the SPI interface will be verified by the VIP.

# BİR SERİ ÇEVRESEL ARAYÜZ FİKRİ MÜLKİYETİNİN EVRENSEL DOĞRULAMA METHODU İLE DOĞRULANMASI

## ÖZET

Günümüzde tasarlanan elektronik sistemlerin karmaşıklığının artması sebebiyle, elektronik sistem tasarım endüstrisi pazara sunma süresi ve tasarım kalitesi zorlukları ile baş etmeye çalışmaktadır. Birini diğerinin pahasına elde etmek çok yaygındır, ancak bu ödün verme kaçınılmaz değildir. "Doğru doğrulamaya" odaklanmak hem üretkenliği hem de kaliteyi artırabilir. Bireysel bir fikri mülkiyet (Intellectual Property - IP) bloğundan bir yonga üstü sisteme (System on Chip – SoC) herhangi bir uygulamanın başarılı bir şekilde tasarlanması, doğru doğrulamaya bağlıdır. Yonga düzeyinden kart düzeyine ve son olarak sistem düzeyine her geçişte, hatalı bir yongayı tespit etmenin maliyeti 10 kat artar. Bazen doğru doğrulama metodolojisini yargılamak kolay değildir ve yanlış olanı seçmek daha sonra sorunlara neden olabilir. Doğrulama IP'si (Verification IP - VIP) doğru yargıya varabilmek için araçlar sağlar.

VIP, temel tasarımın farklı soyutlama düzeylerinde bir kullanıcı etkileşimi aracı sağlayan bir modelden başka bir şey değildir. Tanımlamasını ve doğrulama metodolojisini değerlendirmeyi içeren doğru VIP'yi seçmek, bir tasarım IP'si seçmek kadar zordur. Doğru metodoloji, yeniden kullanılabilirliği, hata ayıklama ve hata düzeltme kolaylığını ve bakımı artırırken altta yatan karmaşıklığı soyutlama yeteneğini geliştirir. Kalıcı bir VIP'nin nasıl oluşturulacağını anlamak, değişen teknolojiler ve pazar koşulları göz önüne alındığında bir zorluktur.

Seri Çevresel Arayüz (Serial Peripheral Interface - SPI), senkron bir seri haberleşme arayüzüdür. SPI, bir usta/çırak ilişkisi içinde çift yollu bir haberleşme düzeni sağlar. Bilgi, ustanın ürettiğin bir saat sayesinde ustadan çırağa ya da çıraktan ustaya iletilecek şekilde aktarılır. Bu iletişim, ustanın ürettiği saatin yükselen ya da alçalan kenarlarına entegre edilmiştir. SPI, yükselen ya da alçalan kenarlarda bilgi iletimi sağlaması için 4 farklı modda çalışmaktadır. Bilgi, Usta Giriş-Çırak Çıkış(MISO) ve Usta Çıkış-Çırak Giriş(MOSI) hatları üzerinden, eşzamanlı olarak aktarılır. Ayrıca birden fazla çırak ile çalışmak SPI protokolünde mümkündür. Usta, Çırak Seçim(Slave Select-SS) biti sayesinde hangi çırağa bilgi aktaracağını ya da bilgi toplayacağını seçebilir.

Bu projede, daha önceden tasarlanmış bir SPI Master-Slave arayüzü kullanılacaktır. Daha sonra bu tasarlanmış modülün doğrulanması için bir VIP tanımlanacak ve VIP kullanılarak SPI modülü doğrulanacaktır.

### **1. INTRODUCTION**

In this project, a digital circuit design is verified by using Universal Verification Methodology (UVM) [1]. UVM is a regulated methodology and has many advantages for the engineers and it is very reliable. Main purpose of this project is to learn and perform the UVM methodology and create a verification environment. Since the main goal is to create a verification environment, a previously designed interface is used as Serial Peripheral Interface Intellectual Property (SPI IP) in this project [2]. This SPI IP is an SPI Master-Slave interface and is designed by using Verilog [3] and SystemVerilog [4] hardware languages. In order to create a verification environment, SystemVerilog and UVM is learnt and implemented. The design code is examined and the signals are defined and connections are made accordingly to the verification environment.

The design is simulated in a simulation tool, QuestaSim [5] and tested by defining input values and signals. Design's simulation behavior is explained in the SPI IP section.

After that, by using UVM, a verification environment is created and the design is tested by using the Design Verification Kit (DVKit) program [6]. QuestaSim simulation tools is also used and two simulation results are compared. UVM's class library, hierarchy and UVM's phases, as well as all the components that are created and used in the verification environment, all the verification steps and the simulation results are explained in the Verification of SPI IP by using UVM section.

#### 2. BACKGROUND INFORMATION

#### 2.1. Verification

The method of checking and confirming the digital circuit design works as intended is called verification. The verification process includes building a test environment by using hardware description languages (HDL) and simulating the design by using various simulators [7].

The main goal of the verification is detecting mistakes. Each digital circuit design has its task, verification engineers have to check and verify that the task is completed as expected. For that, verification engineers build a test environment to show that expected and simulated results are matching.

Checking and confirming the digital circuit design for its accuracy and verifying its reliability are crucial. Therefore, it is inevitable that digital system designs need to be verified.

#### 2.2. Universal Verification Methodology (UVM)

Universal Verification Methodology (UVM) is a regulated methodology for verifying digital circuit designs. UVM is a set of class libraries characterized using the syntax and semantics of SystemVerilog. Its primary goal is to create verification environments that are reusable and arranged well. Before UVM, verification languages like SystemVerilog, e [8] and Vera [9] were used to verify designs. Also, Open Verification Methodology (OVM) were used as verification methods [10]. However, as the complexity of the digital circuit designs increased, verification of these systems with these methods and languages became more and more challenging. Initially, UVM is derived from OVM and promoted by vendors like Synopsys [11], Cadence [12] and Mentor [13]. The main advantage of UVM is the UVM class library. UVM class library is written in SystemVerilog language and it provides particular mission for each component. For instance, a driver class is only in charge of driving signals to the design whereas a monitor class just monitors the design interface and does not drive signals. This feature can be achieved with UVM's class hierarchy. With class hierarchy, each component and sub-component have different responsibilities and can updated separately. Creating a verification environment by using SystemVerilog language is simple but updating and changing each component can be hard. However, with UVM, creating and changing the verification environment are both uncomplicated and easy. Thus, UVM class library and class hierarchy is making the verification environments reusable and making them neat, not complex for the users.

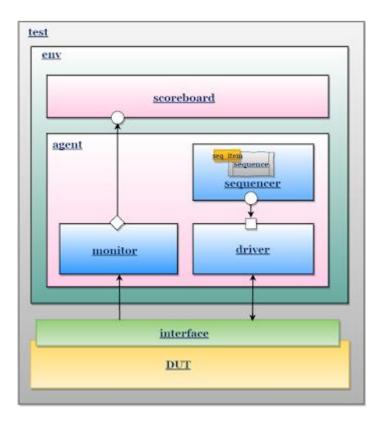

#### 2.2.1. Verification Environment

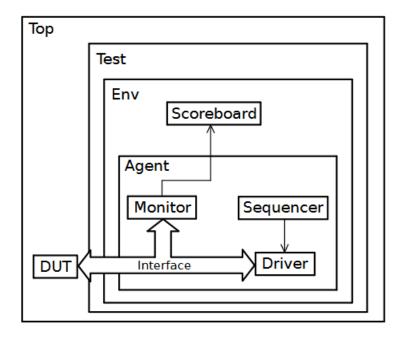

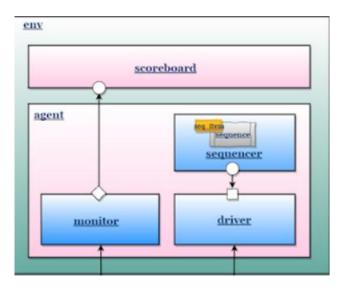

For the verification of a digital circuit design, a verification environment is needed. This environment is called testbench and it includes all the verification components. This testbench will communicate with the DUT (Device Under Test) by using interface. In Figure 2.1, UVM testbench structure is shown. It also includes the interface connection between DUT and the testbench. All the components of this testbench will be explained later. UVM class library, class hierarchy, UVM phases will be used for the creation of the verification environment [20].

Figure 2.1: UVM Testbench Structure [20]

#### 2.2.2. UVM Classes

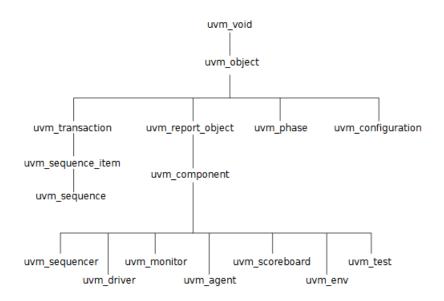

As previously mentioned, UVM class library provides great advantages. The library makes it easy to edit and update each component separately, without having to change the whole testbench. A class tree of UVM classes can be seen down below in Figure 2.2.

Figure 2.2: UVM Class Tree [20]

Uvm\_object class is the core class for the all UVM data and hierarchical classes. All the components and transactions are derived from uvm\_object. Its main duty is to give description to the methods for universal applications like create, copy, compare, print and record [21].

Uvm\_component class is the origin core class for UVM components. All UVM components are derived from uvm\_component. Uvm\_component provides hierarchy interface to search and travel through component hierarchy. All the verification components are derived from uvm\_component class such as uvm\_driver, uvm\_agent, uvm\_monitor etc. Besides hierarchy interface, uvm\_component also grants phasing, reporting, transaction recording and factory interfaces [22].

UVM components and the UVM transaction classes will be explained later.

#### 2.2.3. UVM Phases

UVM phases are coordinated structures for the verification environment. Every verification component pass through UVM phases. Every time a new component is created, the simulation of the verification environment runs through UVM phases to build, compose and connect the testbench component hierarchy [20]. The most essential phases can be seen in Figure 2.3.

Figure 2.3: UVM Phases [20]

Build phase creates testbench components and establish their instances.

Connect phase connects verification components, for instance, it connects driver component to sequencer component.

Run phase is the primary phase where the simulation is carried out.

Report phase demonstrates the result of the simulation [20].

### 2.2.4. Transaction Level Modeling (TLM)

Transaction Level Modeling (TLM) is an interface structure that transfers the created transactions between the components. This transfer is achieved by exclusive ports called TLM interfaces. This modeling sets apart components from each other, if one component is updated, other components that are connected to this component are not affected [44].

TLM library comes with transaction-level interface, ports, imports, exports and analysis ports. In Figure 2.4, a simple connection between ports of components can be seen.

As an example, driver component uses a TLM port, seq\_item\_port, to initiate communication with sequencer. With functions like get\_next\_item and item\_done, this communication can be started and finished.

Another example is in the monitor class. Monitor class uses the analysis port (uvm\_analysis\_port) to call the write function. This write function essentially writes the data that is observed in monitor to the analysis port. Any component that is connected to this analysis port via analysis export can read the data. When monitor class calls the analysis\_port.write(), it checks all the connected exports and calls their write functions. This way scoreboard or subscriber components can read and write the data that is observed in monitor.

Figure 2.4: Transaction transfer via TLM ports [44]

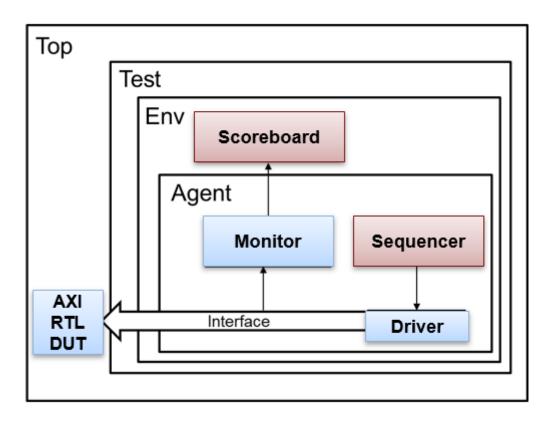

### 2.2.5. Top Block and Interface

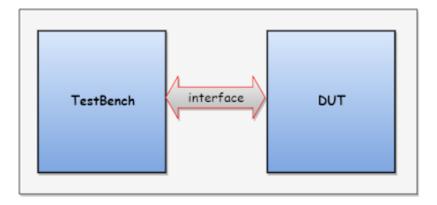

In order to connect the testbench and DUT, two components are required. These are top block and the interface. The top block establishes instances of the DUT and the testbench and the interface connects them. The interface contains all the signals of the DUT. Other components such as driver and monitor, as well as the DUT will be attached to the interface [23]. Figure 2.5 shows the simple connection between testbench and the DUT via interface.

In order to connect to interface to the DUT, virtual interface object is established in top block, then the virtual interface is linked with the DUT that is instantiated in the top block as well.

As mentioned before, interface holds the signals, and allows the user to file and check the transactions transferred between the testbench and the DUT in top block. Since all the data covered in the interface, it is a simple way to establish communication this way.

Figure 2.5: Connection between testbench and DUT via interface [24]

#### 2.2.6. Components

### 2.2.6.1. Transaction

One of the basics of the verification of a digital circuit design is to create data packages. These data packages are sent to the DUT to be processed. The smallest of these data packages or items are called transactions. Usually, the driver class handles signal transfers at the bit layer, but when an 8-bit of a package is needed to be transferred to the DUT, a transaction class is needed [25].

A transaction is a class object and it develops from uvm\_transaction or uvm\_sequence\_item classes. Transaction class carries all the data necessary to create the transmissions between the other components. Transactions are the least possible amount of data can be transmitted and can be carried out by the verification environment as can be seen in Figure 2.6.

Figure 2.6: Transaction Transfer Scheme [26]

#### 2.2.6.2. Sequence and Sequencer

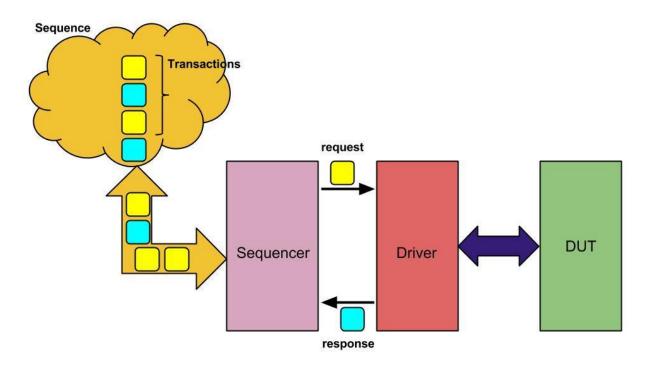

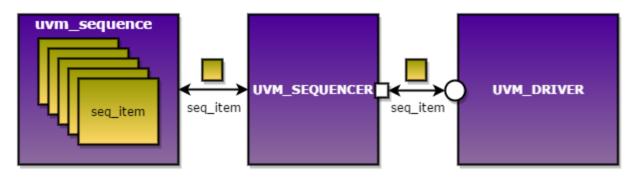

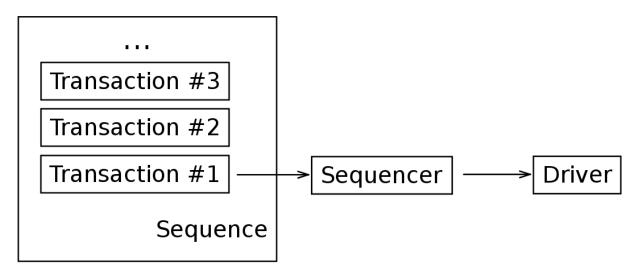

Sequence class is the class that creates sequences from the previously generated transactions. It extends from uvm\_sequence class. These sequences are basically data item combinations, sequence class combines transactions in many ways to generate different outcomes. After that, these sequences are transferred to the driver via sequencer class. Sequencer class extends from uvm\_sequencer in order to establish a communication with the driver [25]. This communication establishment can be seen in Figure 2.7.

Figure 2.7: Sequence-driver communication via sequencer [27]

# 2.2.6.3. Driver

Driver is responsible for sending created transactions to the DUT. Driver gets those transactions, changes them into bit-level actions, and drives the data into the DUT [28]. This structure can be seen in Figures 2.8 and 2.9.

As seen in Figure 2.7, driver receives the transactions or sequence items from sequencer. This communication is established via some techniques. Driver class has a uvm\_seq\_item\_pull port to receive transactions from sequencer. First, driver calls the get\_next\_item function to start the communication. This function runs until all the transactions are transferred. After that, item\_done function is called by the driver in order to stop the communication.

Figure 2.8: Transaction transfer from sequence to driver [25]

| TestBench_Top |                    |

|---------------|--------------------|

| test          |                    |

| env           |                    |

| generator     | interface<br>→ DUT |

|               |                    |

Figure 2.9: Transaction transfer from driver to DUT [29]

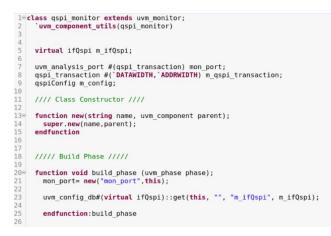

#### 2.2.6.4. Monitor

Monitor is a class that inspects and monitors the communication between the DUT and the testbench. It shows the results from the DUT and displays them to the user. Monitor is a static component, that means it does not send any transactions to any component, its only job is to convert the signals that are sent from the DUT to purposeful data, and then these data will be assessed by other components [30]. Monitor's location and its connections between other components can be seen in Figure 2.10.

Monitor class has an analysis port to allow the users to declare the data to other components such as subscriber and scoreboard. Data is not driven by the monitor, translated data is simply read by the subscriber or scoreboard, in order to compare and verify the result. This communication is established via the analysis port.

Figure 2.10: Monitor in a testbench [31]

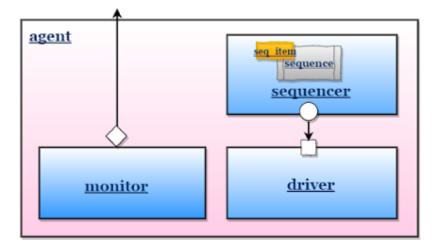

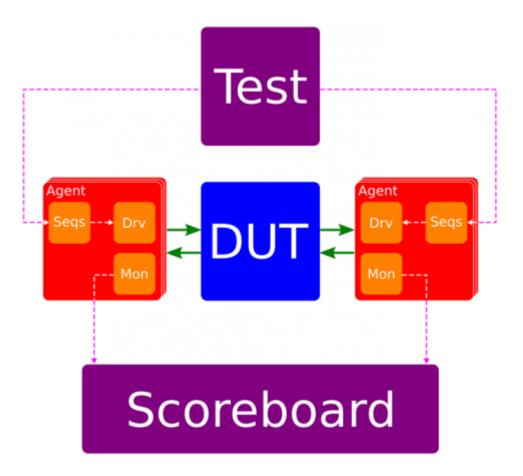

#### 2.2.6.5. Agent

Agent is class that contains all the previous components, driver, monitor and transaction. In Figure 2.11, agent class connects these components to each other and makes the connection to the scoreboard component. It defines the component ports, such as slave and master driver ports, it also allows the user the select the specific driver. Agent class does not need a run phase. All the components established in the build phase and connected in the connect phase. When the agent class is activated by UVM\_ACTIVE, it starts an if statement to choose the slave or master driver. Then the transactions are sent or received accordingly to the selected driver [32].

Figure 2.11: Agent class [33]

## 2.2.6.6. Environment

Environment class is a very simple class that acts like a capsule, it consists of agents, drivers and all the components that are created for the verification environment as can be seen in Figure 2.12.

Agents and scoreboards/subscribers can be incorporated in test class directly but it is not an ideal solution. Environment class is defined because of the reusability, it is easy to update the structure, if incorporation is done in test class, it would take a lot time to upgrade the files. Created environments can be used for multiple tests. For each test, there would be no need to build the environment and its subcomponents from scratch [34].

Figure 2.12: Environment class [35]

#### 2.2.6.7. Subscriber

Subscriber is class that has a built-in analysis port named analysis\_export which provides access to the write method for receiving transactions. Previously created monitor class has an analysis port which contains write function. With this analysis port, transactions are transferred to analysis components like scoreboard or subscriber. Subscriber basically acts as an audience for the analysis port, they "subscribe" to a communicator and acquires and then prints the results of the received transactions whenever they are published [36].

### 2.2.5.8. Scoreboard

Scoreboard class is created to validate and verify the design. It examines the results from the DUT, and compares them with the anticipated results. Scoreboard obtains the transactions by checking the monitor's analysis port [40]. Scoreboard's location in the testbench structure, as well as its connection to the monitor and DUT can be seen in Figure 2.13.

Scoreboard class uses its export port to read the data from monitor's analysis port. Monitor class calls the analysis\_port.write(), it checks all the connected exports and calls their write functions. After that, scoreboard can analyze and verify the data.

Figure 2.13: Scoreboard's connections [43]

### 2.2.6.9. Test

Test class is created to run the tests for the design. These tests are built by user and many different tests can be applied to the design since test class contains environment class and all the other components. That is why this method is chosen since it allows the user to reuse the verification environment without changing the all structure [41].

As mentioned, test class capsules the environment class so many different sequences can be carried out by the user, either in the same test via using different sequencers or operating different tests. That way, users validate the design by running different sequence combinations.

Created tests called and carried out in top block of the testbench by using run\_test function. As specified before, with this arrangement, more than one test and different sequence combinations can be achieved for different outcomes and the verification of the design would be more valid. Test class encapsulates environment and other classes as can be seen in Figure 2.14.

Figure 2.14: Test class [42]

#### 2.3. Serial Peripheral Interface (SPI)

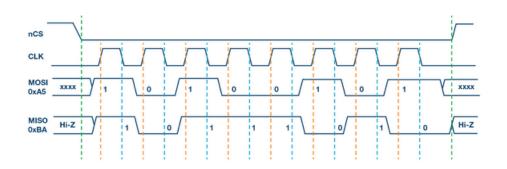

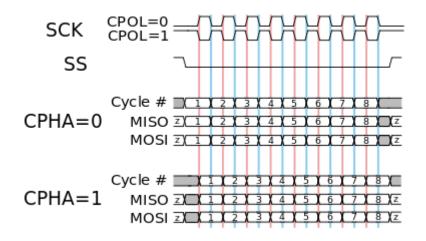

Serial Peripheral Interface (SPI) is a synchronous serial communication interface. SPI devices communicate in full duplex mode using a master-slave structure. The data from the master or the slave is adjusted on the rising or falling clock edge. Master and slave can send data simultaneously. SPI has 4 signals. These are Clock (SCLK, CLK), chip select/slave select (CS, SS), master-in slave-out (MISO) and master-out slave-in (MOSI). MOSI and MISO are the data lines. MOSI sends data from the master to the slave and MISO sends data from the slave to the master. Clock signal is produced by the master. Data is carried between the master and the slave, and synchronized to the clock that is created by the master. To start the SPI communication, the master sends the clock signal and chooses the slave by activating the chip select signal. Throughout the communication, the data is synchronously sent and acquired via MOSI and MISO lines, since SPI is a full-duplex interface. There are 4 modes of the SPI communication. The master can choose the clock polarity (CPOL) or the clock phase (CPHA) to determine these modes. The CPOL bit configures the polarity of the clock signal during the ineffective case. The CPHA bit picks the clock phase. The rising or falling clock edge is used to examine and/or move the data [37]. SPI modes with CPOL and CPHA can be seen down below in Figures 2.15, 2.16, 2.17 and 2.18.

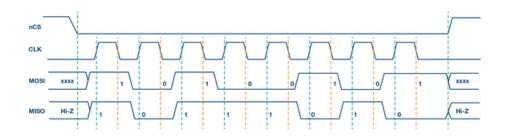

Figure 2.15: SPI Mode 0, CPOL=0, CPHA=0, CLK idle state=low [37]

In SPI Mode 0, clock polarity is 0, which displays that idle state of the clock signal is low. Clock phase is 0, which implies that the data is examined on the rising edge and then the data is transferred on the falling edge of the clock signal as can be seen in Figure 2.15.

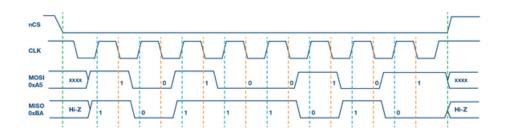

Figure 2.16: SPI Mode 1, CPOL=0, CPHA=1, CLK idle state=low [37]

In SPI Mode 1, clock polarity is 0, which displays that idle state of the clock signal is low. Clock phase is 1, which implies that the data is examined on the falling edge and then the data is transferred on the rising edge of the clock signal as can be seen in Figure 2.16.

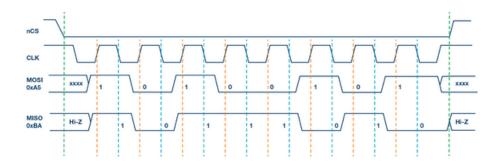

Figure 2.17: SPI Mode 2, CPOL=1, CPHA=0, CLK idle state=high [37]

In SPI Mode 2, clock polarity is 1, which displays that idle state of the clock signal is high. Clock phase is 0, which implies that the data is examined on the falling edge and then the data is transferred on the rising edge of the clock signal as can be seen in Figure 2.17.

Figure 2.18: SPI Mode 3, CPOL=1, CPHA=1, CLK idle state=high [37]

In SPI Mode 2, clock polarity is 1, which displays that idle state of the clock signal is high. Clock phase is 1, which implies that the data is examined on the rising edge and then the data is transferred on the falling edge of the clock signal as can be seen in Figure 2.18. An SPI diagram, including all the modes can be seen down below in Figure 2.19.

Figure 2.19: SPI diagram with all modes [38]

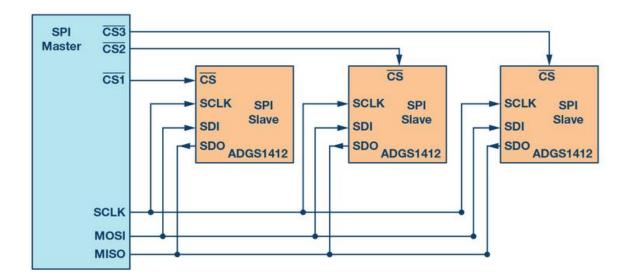

One SPI master can work with numerous slaves. These slaves can be linked in regular mode or daisy-chain mode. Figure 2.20 shows the regular mode structure. In regular mode, every slave has its own chip select signal from the master. When the chip select signal is activated by the master, MOSI and MISO lines are ready to use for the clock and the data transfer for chosen slave. If master activates more than one chip select, it cannot recognize which slave is sending data and the data on MISO line becomes distorted [37].

Figure 2.20: Regular SPI mode structure [37]

In daisy-chain mode, in Figure 2.21, the slaves arranged such that the chip select signal for the slaves is connected to each other and data flows from one slave to the next. In this setup, each slave gets the exact SPI clock simultaneously. First slave obtains the data from the master and passes on the next slave until all slaves get the data. It is not as efficient as regular mode, because number of the clock cycles needed to send data is significantly more in daisy-chain mode [37].

Figure 2.21: Daisy-chain mode [37]

There are some advantages and disadvantages of SPI, compared to other communication protocols like I2C (Inter-Integrated Circuit) [14] and UART (Universal Asynchronous Receiver Transmitter) [15]. First, SPI has some advantages over its counterparts. Unlike UART, SPI has no start and stop bits, data is transmitted repeatedly without disruption. SPI's slave communication method is not as complex as I2C's slave communication method. SPI has greater data transfer percentage that I2C. Also, SPI has MISO and MOSI lines, both of these lines can be used for transmitting and receiving data simultaneously. However, SPI has some disadvantages as well. SPI uses four wires whereas I2C and UART use two wires. Since SPI has no start or stop bits, no confirmation on the delivery of the data, I2C has that feature. Also, unlike UART, SPI has no parity bit so that it cannot inspect the mistakes in the data. Finally, although SPI supports multiple slaves, it only permits one master [39].

### 3. Verification and Simulation Tools

Creating a verification environment, simulating the design and comparing the results require some tools. In this project, an Integrated Development Environment (IDE) is needed for developing the verification environment and for the simulations, a simulation environment is needed. For IDE, DVKit is used and for simulator, QuestaSim is chosen.

# 3.1. Design Verification Kit (DVKit)

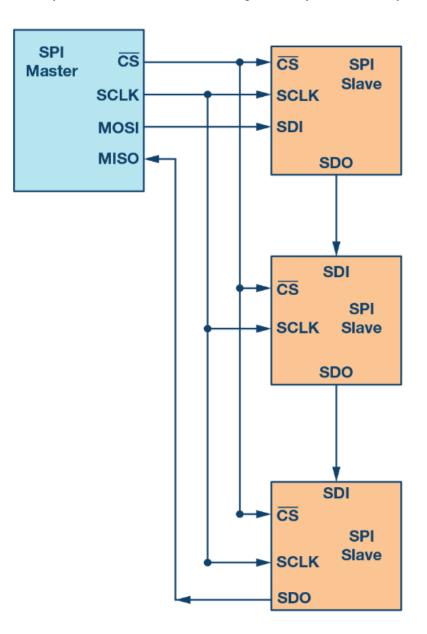

DVKit is an IDE for design and verification engineers. IDE provides engineers with extensive tools for the software development. DVKit helps the verification engineers to handle the verification environment which consist of SystemVerilog and UVM. It comes with an editor, SystemVerilog Editor (SVEditor), for Verilog and SystemVerilog as well as UVM. It also comes with C development tools and Webtools for development but these are not necessary to create a verification environment. These tools can be activated by using the Eclipse plugin since DVKit's IDE is Eclipse-based [6]. Main interface of the DVKit can be seen in Figure 3.1.

Figure 3.1: DVKit interface [6]

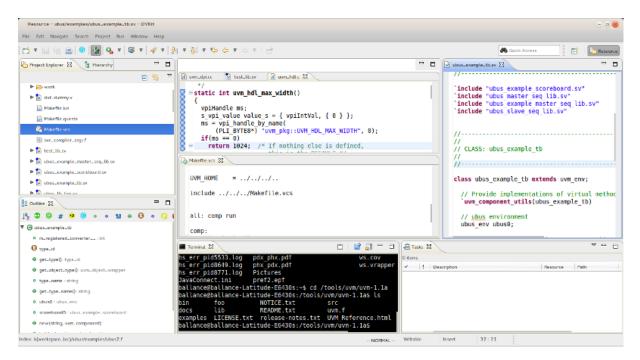

# 3.2. QuestaSim

Questa is a verification tool that includes an integrated platform called QuestSim. Questa is owned and developed by Mentor Graphics. QuestaSim can perform advanced verification of electronic systems with high efficiency. Administration and debugging facilities are embedded in QuestaSim structure [5]. It is based on ModelSim [16] tool, which is also owned by Mentor Graphics. Main difference between ModelSim and QuestaSim is, QuestaSim supports SystemVerilog and UVM, but ModalSim does not, which is why in this project, QuestaSim is used for the simulations -.

QuestaSim's main interface can be seen in Figure 3.2.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Questa             | Sim 10.6       | 0   |                                    |                   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\odot$ $\otimes$ $\otimes$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-----|------------------------------------|-------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <u>File Edit View Compile Simulate</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Add Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T <u>o</u> ols Layo <u>u</u> t I                                              | Boo <u>k</u> marks <u>W</u> ind                                                                                   | ow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |                |     |                                    |                   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |

| 🖹 • 🚅 🖬 🚿 🚳   🗴 🗞 🎕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2210.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Help                                                                          | 34                                                                                                                | ۵ 🖄 🗳                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 🔉 🕱 🛛 😼 🕯          | E- 🛊 🖛 🕪       | 1   | 100 ps 🔹 🖫 🖫                       | 🕺 😃   🖄 🚰 📆       | 0 1        | æ‡ ±-æ-±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

| Layout Simulate 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ColumnLayout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Default                                                                       |                                                                                                                   | . 🖉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • 🚳 - 🧐 - 🖓        | 3 I O M        | A D | i 🖉 🕺 X4 ÞX 🖻 🕺                    |                   |            | R Q R L L R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

| 🕼 sim - Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | ±              | đX  | 🔁 Objects 🚃 🗄                      |                   | × h]:rc/ba | ase/uvm_root.svh (/uvm_p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | okg) - Default 🛲 🛨 🛃 🗙      |