## ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY

# IMPLEMENTATION OF A SOC BY USING LOWRISC PROCESSOR ON AN FPGA FOR IMAGE FILTERING APPLICATIONS

**SENIOR DESIGN PROJECT**

Bartu SÜRER

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

JANUARY 2019

## **ISTANBUL TECHNICAL UNIVERSITY ELECTRICAL-ELECTRONICS FACULTY**

## IMPLEMENTATION OF A SOC BY USING LOWRISC PROCESSOR ON AN FPGA FOR IMAGE FILTERING APPLICATIONS

## **SENIOR DESIGN PROJECT**

Bartu SÜRER (040160706)

# ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

Project Advisor: Assoc. Prof. Dr. Sıddıka Berna ÖRS YALÇIN

JANUARY 2019

We are submitting the Senior Design Project Report entitled as "IMPLEMENTATION OF A SOC BY USING LOWRISC PROCESSOR ON AN FPGA FOR IMAGE FILTERING APPLICATIONS". The Senior Design Project Report has been prepared as to fulfill the relevant regulations of the Electronics and Communication Engineering Department of Istanbul Technical University. We hereby confirm that we have realized all stages of the Senior Design Project work by ourselves and we have abided by the ethical rules with respect to academic and professional integrity.

**Bartu SÜRER** (040160706)

Project Advisor: Assoc. Prof. Dr. Sıddıka Berna ÖRS YALÇIN

.....

vi

## FOREWORD

I would like to thank to my mentor Assoc. Prof. Dr. Sıddıka Berna Örs Yalçın who helped me to find this project and who supported me in all my mistakes, to reach flawless success and at least work as much as I to complete my project successfully. Secondly, I would like to offer my gratitude to my mentor Res. Assist. M.Sc. Latif Akçay, who gave his endless support and even sacrificed his own time in every stage of the project. Without him, I would never find my way in this project. Finally, I would like to emphasize that I owe to my friends, my girlfriend Serra Önder for her endless support and my family who has the biggest role on my successes for my entire life.

January 2019

Bartu SÜRER

# **TABLE OF CONTENTS**

# Page

| FOREWORD                                                                                                                   |                            |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------|

| TABLE OF CONTENTS                                                                                                          | ix                         |

| ABBREVIATIONS                                                                                                              | xi                         |

| LIST OF TABLES                                                                                                             | xiii                       |

| LIST OF FIGURES                                                                                                            | xv                         |

| SUMMARY                                                                                                                    | xvii                       |

| ÖZET                                                                                                                       | xix                        |

| 1.INTRODUCTION                                                                                                             |                            |

| 1.1 Basic Information And Concepts                                                                                         |                            |

| 1.1.1 Open source CPUs                                                                                                     |                            |

| 1.1.1.1 Amber                                                                                                              |                            |

| 1.1.1.2 Leon                                                                                                               |                            |

| 1.1.1.3 OpenSPARC                                                                                                          |                            |

| 1.1.2 RISC-V                                                                                                               |                            |

| 1.1.2.1 RISC-V compiling tools                                                                                             |                            |

| 1.1.3 LowRISC                                                                                                              |                            |

| 1.1.3.1 Rocket-Core view                                                                                                   |                            |

| 1.1.4 Image processing and filters                                                                                         |                            |

| 1.1.4.1 Kernel                                                                                                             |                            |

| 1.1.4.2 Convolution operation                                                                                              |                            |

| 1.1.5 General flow of project                                                                                              |                            |

| 1.2 Literature Review                                                                                                      |                            |

| 1.2.1 Literature review at Istanbul Technical University                                                                   |                            |

| 1.2.2 Literature review at Turkey                                                                                          |                            |

| 1.2.3 Global Literature review                                                                                             |                            |

| 2.IMPLEMENTING LowRISC PROCESSOR ON AN FPGA                                                                                |                            |

| 2.1 Gathering Required Environment                                                                                         |                            |

| 2.1.1 Installation of cable drivers                                                                                        |                            |

| 2.1.2 Installation of Cmake                                                                                                |                            |

|                                                                                                                            |                            |

| 2.1.3 Downloading LowRISC chip git repository                                                                              |                            |

| 2.1.4 Installing RISC-V GNU tookhain                                                                                       |                            |

| 2.2 Installing Linux to lowRISC                                                                                            |                            |

| 2.3 Peripherals of system                                                                                                  |                            |

| 2.4 Implementing image filter algorithms to lowRISC                                                                        |                            |

| 2.4.1 PPM format                                                                                                           |                            |

| 2.4.2 Converting PNG to PPM.                                                                                               |                            |

| 2.4.3 Sending input image to lowRISC                                                                                       |                            |

|                                                                                                                            |                            |

| 2.4.4 C code for filters                                                                                                   |                            |

| 2.4.4 C code for filters<br>2.4.4.1 Common parts of filter in codes                                                        |                            |

| <ul><li>2.4.4 C code for filters</li><li>2.4.4.1 Common parts of filter in codes</li><li>2.4.4.2 Red Only filter</li></ul> |                            |

| <ul> <li>2.4.4 C code for filters</li></ul>                                                                                |                            |

| <ul> <li>2.4.4 C code for filters</li></ul>                                                                                | 36<br>37                   |

| <ul> <li>2.4.4 C code for filters</li></ul>                                                                                | 36<br>37<br>38             |

| <ul> <li>2.4.4 C code for filters</li></ul>                                                                                | 36<br>37<br>38<br>40       |

| <ul> <li>2.4.4 C code for filters</li></ul>                                                                                | 36<br>37<br>38<br>40<br>41 |

| 2.4.4.9 Gaussian Blur filter                      | 43 |

|---------------------------------------------------|----|

| 2.4.5 Autamatization of filtering image algorithm | 44 |

| 3.REALISTIC CONSTRAINTS AND CONCLUSIONS           |    |

| 3.1 Practical Application of this Project         | 49 |

| 3.2 Realistic Constraints                         | 49 |

| 3.2.1 Social, environmental and economic impact   | 49 |

| 3.2.2 Cost analysis                               |    |

| 3.2.3 Standards                                   |    |

| 3.2.4 Health and safety concerns                  | 50 |

| 3.3 Future Work and Recommendations               |    |

| REFERENCES                                        |    |

| CURRICULUM VITAE                                  | 53 |

# **ABBREVIATIONS**

| ALU  | : Arithmetic Logic Unit                                             |

|------|---------------------------------------------------------------------|

| CPU  | : Central Processing Unit                                           |

| FPGA | : Field Programmable Gate Array                                     |

| FPU  | : Floating Point Unit                                               |

| ISA  | : Instruction Set Architecture                                      |

| OS   | : Operating System                                                  |

| PC   | : Personal Computer                                                 |

| RISC | : Reduced Instruction Set Computing                                 |

| RTL  | : Register Transfer Level                                           |

| SoC  | : System on Chip                                                    |

| VHDL | : Very High –Speed Integrated Circuit Hardware Description Language |

xii

# LIST OF TABLES

# Page

| Table | 1.1 : Some | cores that used RISC-V ISA [2] | 3 |

|-------|------------|--------------------------------|---|

| Table | 1.2 : Some | SoCs that used RISC-V ISA [2]  | 4 |

| Table | 1.3 : Some | basic RISC instructions [9].   | 5 |

# LIST OF FIGURES

# Page

| Figure 1.1: RISC-V GCC toolflow. Greens are input files and blues are output fi  |      |

|----------------------------------------------------------------------------------|------|

| [9]                                                                              |      |

| Figure 1.2 : Top view of lowRISC SoC [10]                                        |      |

| Figure 1.3 : Instruction cache which includes pcgen and fetch stages [12]        |      |

| Figure 1.4 : Other stages of pipeline [12].                                      |      |

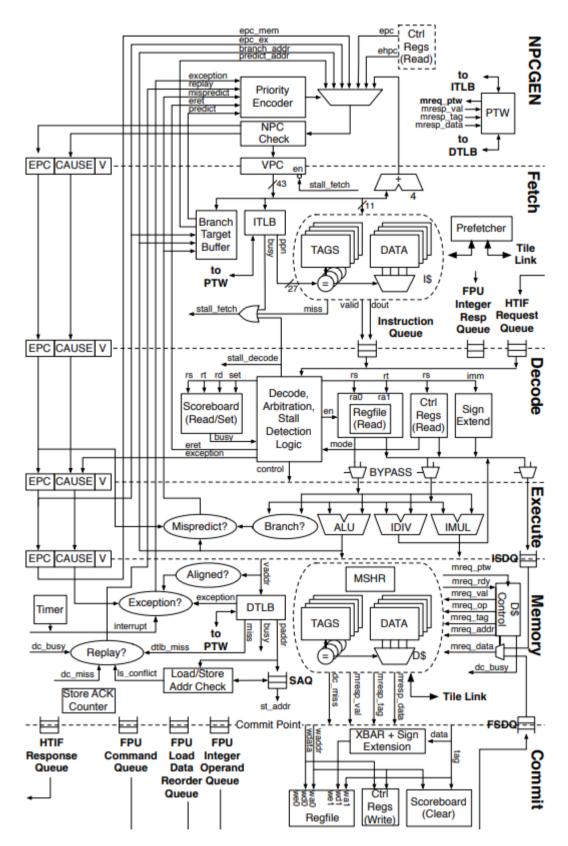

| Figure 1.5 : All pipeline stages in one diagram [9].                             |      |

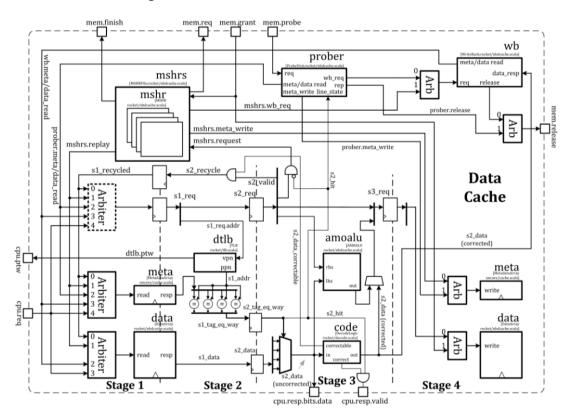

| Figure 1.6 : L1 data cache overview [12].                                        |      |

| Figure 1.7 : General microarchitecture of all system [9].                        |      |

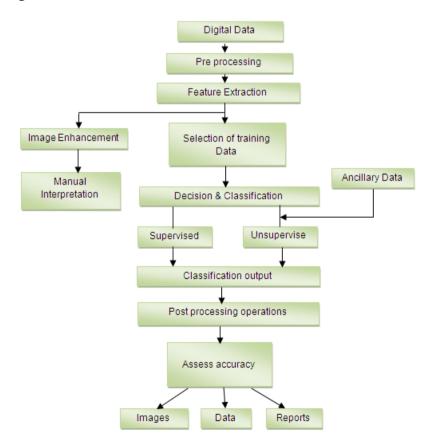

| Figure 1.8 : Image processing algorithm general flow [14]                        |      |

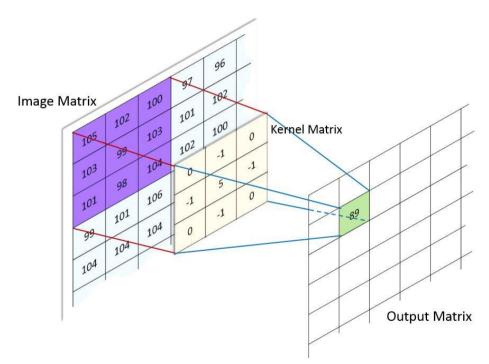

| Figure 1.9 : Convolution operation.                                              | . 12 |

| Figure 2.1 : Bashrc commad window                                                |      |

| Figure 2.2 : 16 GB SD Card                                                       |      |

| Figure 2.3 : After commands worked properly.                                     |      |

| Figure 2.4 : Jumper positions to boot from SD card                               |      |

| Figure 2.5 : Boot screen at VGA display                                          | . 22 |

| Figure 2.6 : Waiting input mode                                                  |      |

| Figure 2.7 : Booting from SD card chosen                                         | . 23 |

| Figure 2.8 : Successfully boot operation started.                                | . 24 |

| Figure 2.9                                                                       | 24   |

| Figure 2.10                                                                      | 25   |

| Figure 2.11 : First stage bootloader output.                                     | . 25 |

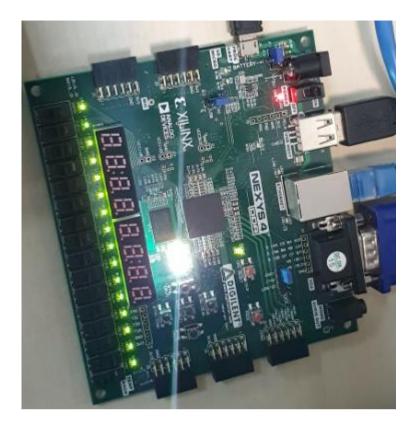

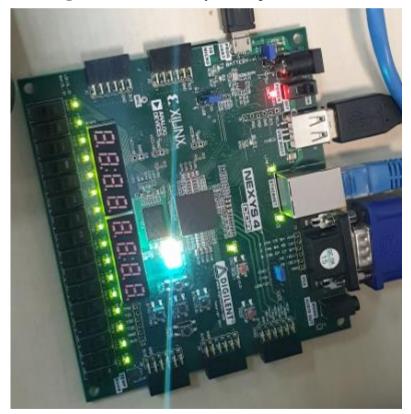

| Figure 2.12 : Hash code of kernel.                                               | 26   |

| Figure 2.13 : There could be some warns. It will continue                        | 26   |

| Figure 2.14 : Other boot informations                                            | 27   |

| Figure 2.15 : Ethernet connection is okey too.                                   | 27   |

| Figure 2.16 : Login screen and first login must be root                          |      |

| Figure 2.17 : Login screen with prompts                                          |      |

| Figure 2.18 : Bash command screen.                                               |      |

| Figure 2.19 : Full peripheral connection.                                        |      |

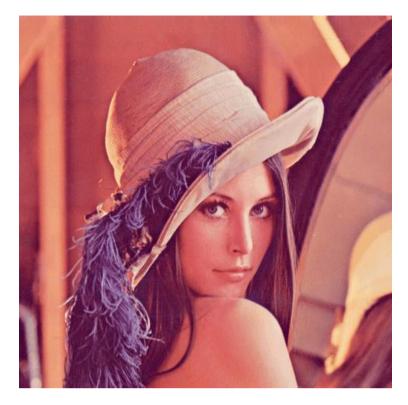

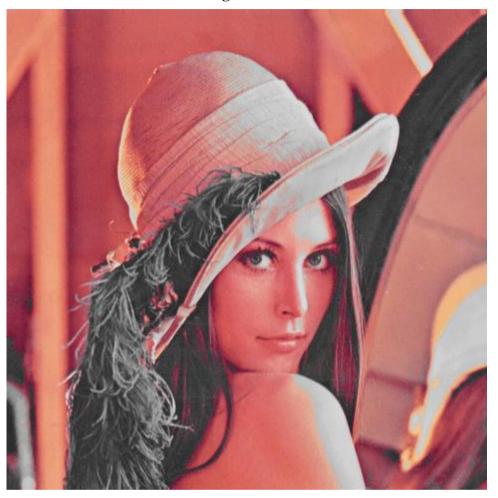

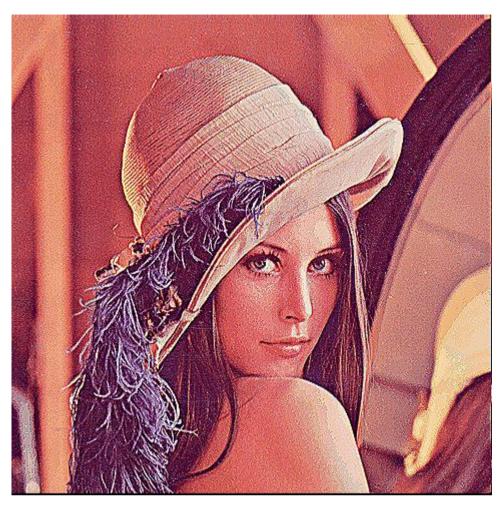

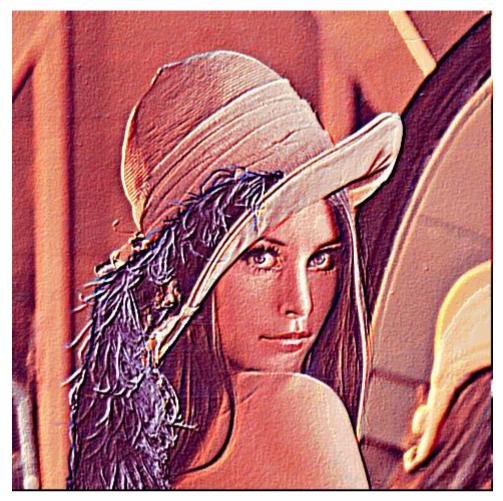

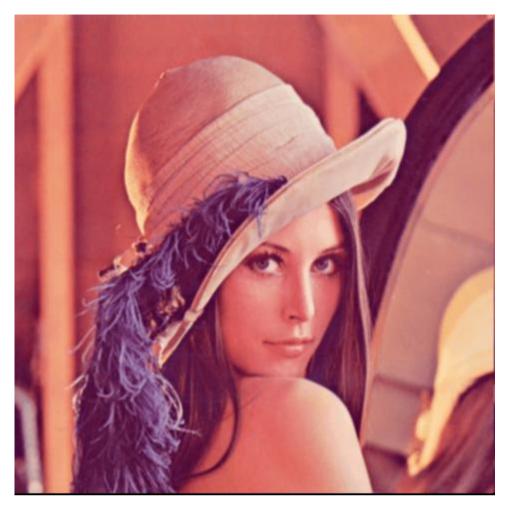

| Figure 2.20 : Example input image                                                | 33   |

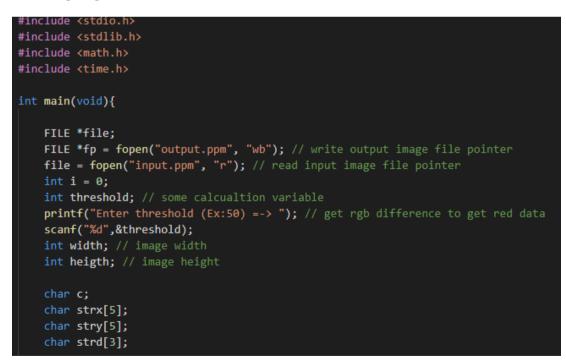

| Figure 2.21 : Reading input and writing output file pointers                     |      |

| Figure 2.22 : Reading image information and writing output file same information |      |

|                                                                                  |      |

| Figure 2.23 : Some variables for rgb datas and reading image and storing to      |      |

| variables.                                                                       | 35   |

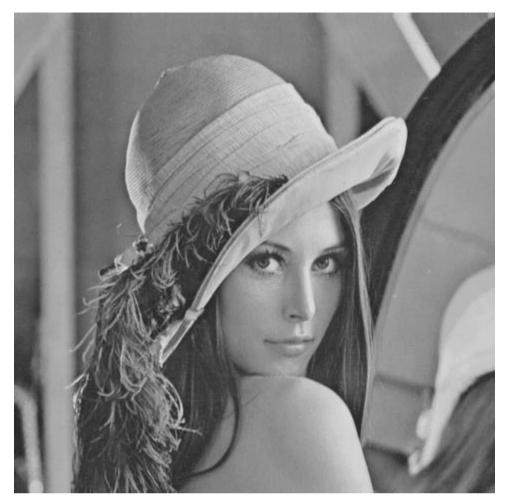

| Figure 2.24 : Grayscale of image if needed.                                      |      |

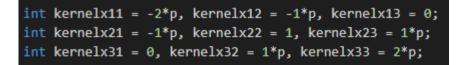

| Figure 2.25                                                                      |      |

| Figure 2.26                                                                      |      |

| Figure 2.27                                                                      |      |

| Figure 2.28                                                                      |      |

| 5                                                                                |      |

| Figure 2.29                                                                    | . 37 |

|--------------------------------------------------------------------------------|------|

| Figure 2.30                                                                    | . 38 |

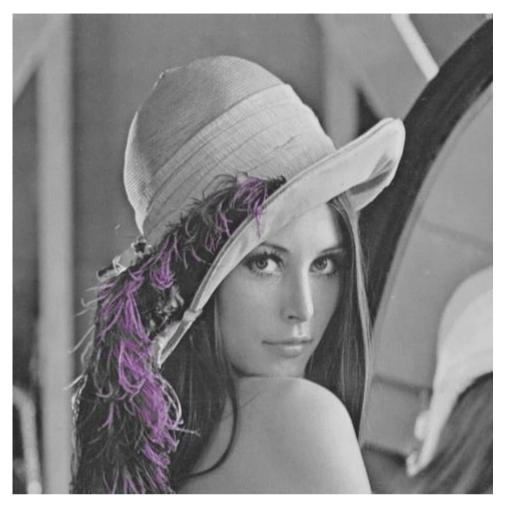

| Figure 2.31 : Horizontal kernel                                                |      |

| Figure 2.32 : Vertical kernel.                                                 | . 38 |

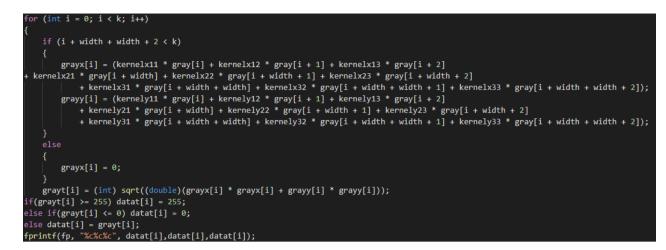

| Figure 2.33 : Convolution operation code and blending operation horizontal and |      |

| vertical lines                                                                 | . 39 |

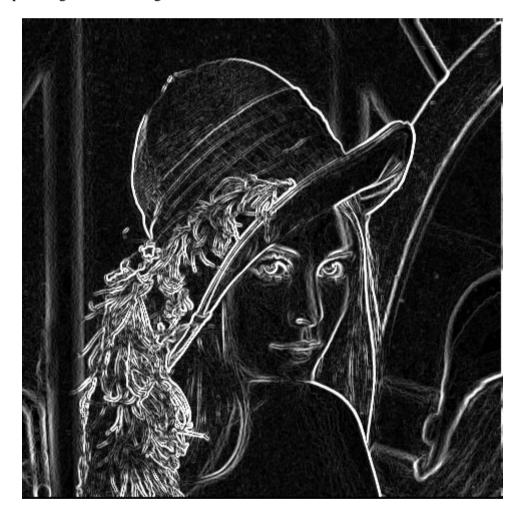

| Figure 2.34 : Sobel operation output.                                          |      |

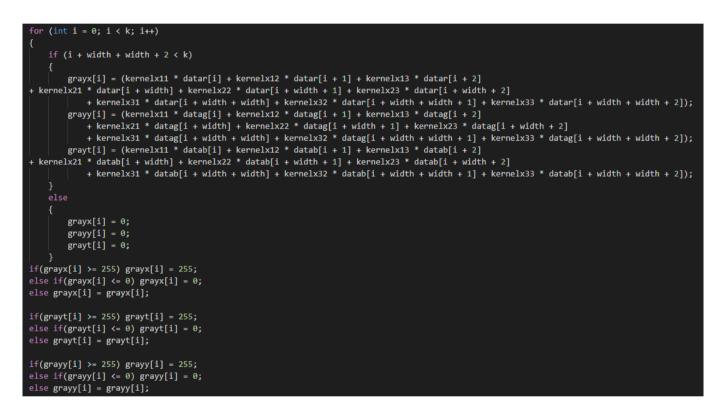

| Figure 2.35                                                                    |      |

| Figure 2.36 : Convulution and reduction of lower 0 and upper 255 values        |      |

| Figure 2.37                                                                    |      |

| Figure 2.38                                                                    |      |

| Figure 2.39                                                                    |      |

| Figure 2.40                                                                    |      |

| Figure 2.41                                                                    |      |

| Figure 2.42                                                                    |      |

| Figure 2.43                                                                    |      |

| Figure 2.44 : Usage of Automatization code.                                    |      |

| <b>LIGHTE A</b> TT TO Suge of Automatization code.                             |      |

## IMPLEMENTATION OF LOWRISC SOC ON FPGA FOR IMAGE FILTERING APPLICATIONS

#### SUMMARY

The rapid increase in technology is one of the major factors that lead to a rapid increase in human needs. In every area of our lives, we now carry out our daily and professional life with the help of machines. For these reasons, the importance of processors that give mind and purpose to machines comes to the fore. But the biggest problem with all the increasing importance is the lack of a standard in the architecture of these processors. Although each company creates its own standard and architectural structure, today there is no architectural structure in which these companies have shared. In addition, large chip manufacturers develop their own chips and software and sell them at high prices. Because chip development requires years of knowledge and research, and at the same time, this process creates high costs. For this reason, countries and institutions that could not create their own chip architecture will benefit from using open source processors instead of purchasing high-priced and non-opensource firms' chips for their smart machines. In this context, open source processors are becoming more and more important in order to be able to benefit economically and to be highly effective in terms of performance / price. In this project, with using "RISC-V" instruction set architecture which was created eight years ago at the University of California, Berkeley and is closely followed by many large companies like Nvidia and Western Digital, based "lowRISC" SoC is aimed to be implemented and image processing algorithms will be executed on that SoC. This SoC created with Rocket cores.

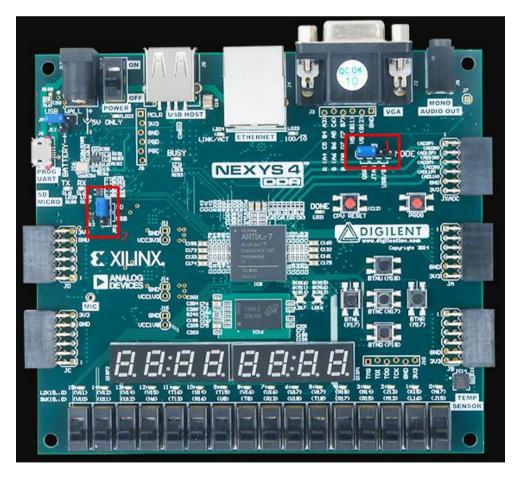

For the implementation of the project, FPGA (field programmable gate series) technology, which is one of the most important blessings offered by the technology to the electronics engineers, is used. In general, the project first deals with the proper operation of the lowRISC chip system on the "Nexys 4 DDR" produced by Xilinx properly. Then, a Linux operating system version which works with lowRISC installed on this chip, certain filters have been applied to the images with pure "C" programming language without installing any additional libraries. For this purpose, Gauss blur filter, Sobel operation filter, Embossing filter, sharpening filter, black-white filter and many more are used in this project, which are essential for image processing applications and which are essential for image feature detection purpose.

As a result, the outcome of the project also shows us the working conditions and cost of a system developed using this processor. Even though we haven't developed an architecture as a country yet, open source processors are shown in this project which will be extremely helpful to us in the technological tools we produce. Here, it is seen that choosing these processors are extremely wise decision for developers in terms of time, price and labor, both for prototyping and technological studies.

## FPGA ÜZERİNDE GÖRÜNTÜ İŞLEME AMACIYLA LOWRISC ÇİP SİSTEMİNİN GERÇEKLEŞTİRİLMESİ

## ÖZET

Teknolojinin hızla artması, insan ihtiyaçlarının da hızla artmasına yol açan büyük etmenlerden biri. Hayatımızın her alanında artık makinelerin yardımlarıyla günlük ve profesyönel hayattaki işlerimizi gerçekleştiriyoruz. Tüm bu sebeple makinelere akıl ve amaç veren işlemcilerin önemi ön plana çıkmaktadır. Ancak tüm artan önemin getirdiği en büyük sıkıntı bu islemcilerin mimarisinde bir standartın olmaması. Her firma kendi standartını ve mimari yapısını oluştursa da, günümüzde bu firmaların ortaklaştığı bir mimari yapı bulunmamakta. Ayrıca büyük çip üreticileri kendi çiplerini ve yazılımlarını geliştirmekte ve bunları yüksek fiyatlarda satmaktadır. Çünkü çip gelistirmek yılların bilgi birikimi ve arastırmasını gerektirmekte ve aynı zamanda bu süreçte yüksek maliyet ortaya çıkarmaktadır. Bu sebeple kendi çip mimarisini oluşturamamış ülkeler ve kurumlar, kendi geliştirecekleri makineler için yüksek fiyatlı ve açık kaynaklı olmayan firmaların çip mimarisini satın almak yerine, açık kaynak kodlu olan işlemcileri kullanmalarında büyük fayda sağlayacaklardır. Bu bağlamda özellikle ekonomik olarak da faydalanabilmek ve performans/fiyat açısından son derece efektif olması için, dünyanın birçok yerinde rövaşta olan açık kaynak kodlu işlemciler git gide önem kazanmakta. Bu projede ise sekiz yıl önce Berkeley'deki California Üniversitesi tarafından geliştirilen, günümüzde de bir çok büyük firma tarafından da (Nvidia, Western Digital) yakından takip edilen "RISC-V" komut seti mimarisi ile oluşturulmuş Rocket çekirdeği tabanlı olan "lowRISC" çip üzeri sistemi çip üzeri sistemi gerçeklenmesi ve üzerinde görüntü işleme algoritmalarının calıstırılması hedeflenmiştir. Bu amaçla görüntü isleme uygulamalarında kullanılan olmazsa olmaz filtrelerden Gauss bulanıklaştırma filtresi, Sobel operasyonu filtresi, Kabartma filtresi, keskinleştirme filtresi, siyah-beyaz filtre ve daha pek çoğu, bu projede gerçekleştirilmiştir.

Projenin gerçekleştirilmesi için, teknolojinin elektronik mühendislerine sunduğu en önemli nimetlerden biri olan FPGA (alan programlanabilir geçit seri) teknolojisi kullanılmıştır. Proje genel olarak önce lowRISC çip üzeri sisteminin, Xilinx firması tarafından üretilen "Nexys 4 DDR" üzerinde kurulması ve çalıştırılmasını ele alıyor. Daha sonra bu çipe kurulan Linux işletim sistemi üzerinde, hiç bir ek kütüphane kurmadan saf "C" programlama dili ile görüntülere belirli filtreler uygulanmıştır. Bu amaçla, görüntü işleme uygulamalarında kullanılan ve görüntünün işlenmesi için gerekli olan özelliklerini ön plana çıkaran, olmazsa olmaz filtrelerden Gauss bulanıklaştırma filtresi, Sobel operasyonu filtresi, Kabartma filtresi, keskinleştirme filtresi, siyah-beyaz filtre ve daha pek çoğu bu projede gerçekleştirilmiştir.

Sonuç olarak, projenin getirisinin de bize gösterdiği sonuç, bu işlemci kullanılarak geliştirilen bir sistemin çalışma şartları ve maliyeti kolayca hesaplanabilir. Henüz ülke olarak bir mimari geliştirmemiş olsak bile açık kaynak kodlu işlemciler, kendi üreteceğimiz teknolojik araçlarda bize son derece yardımcı olacağı bu projede gözler önüne serilmiştir. Burada hem prototiplenmesi hem de teknolojik çalışmalara ayrılacak zaman, fiyat ve emek açısından, bu işlemcilerin geliştiriciler için son derece akıllıca bir seçim olduğu görülmüştür.

#### 1. INTRODUCTION

In this graduation project, firstly the "lowRISC" chip [1], which was created from the open source processors "RISCV" architecture [2], will be implemented on the Nexys4 DDR [3] which belongs to Xilinx and then the image processing algorithm will be run on the Linux operating system which will be run by this process. In addition, the "lowRISC" architecture in the project has been examined in detail and will be explained in this section.

Recently, the increasing trend and need for image processing and machine learning is the main reason for the use of this project and the processor. In this project, the use of image processing algorithms on the system and evaluation of the results will be discussed.

## **1.1 Basic Information And Concepts**

A detailed description of all equipment, tools and software used in the project will be made in this section. It will be stated what each one is and what the purpose serves in the project..

#### 1.1.1 Open source CPUs

Over the years, the word "open source" has only been talked about software in the world of technology [4]. The main reason for this is that developing a software requires less resources than developing hardware. These sources can be listed as basic economic, commercial, time and research studies. However, with the advancing technology nowadays, many developer groups are now less dependent on these resources. In addition, the development of their own architectural structures of large firms and the competition among themselves, these companies do not bring any standard to the chip world. For this reason, the importance and value of open source processors in the last decade has been understood by the big companies that develop other technologies. Some of thems are listed below.

#### 1.1.1.1 Amber

Amber is a processor core that supports the "ARM" architecture and has a 32 bit RISC calculation [5]. The processor is open source and is located on the website of the action called "OpenCores". The Amber processor has an instruction set fully compatible with ARMv2a and has full support by the "GNU toolchain". The reason why the processor has this old version instruction set is that it is not patented by ARM [5].

#### 1.1.1.2 Leon

LEON is a 32-bit CPU microprocessor core, with used the SPARC-V8 RISC architecture and its instruction set designed by Sun Microsystems [6]. It was firstly designed by the European Space Research and Technology Centre, and after that designing the project was continued by Gaisler Research. LEON was written in synthesizable Verilog HDL (Hardware Description Language) [6]. LEON has two different license model, a LGPL/GPLFLOSS license that can be used without any payment for licensing, and other is a proprietary license that can be purchased for integration in a proprietary product [6].

#### 1.1.1.3 OpenSPARC

OpenSPARC is a 64-bit and 32-threaded processor written in verilog in 2005 by Sun Microsystems' register-transfer level (RTL) [7]. OpenSPARC with two different models, UltraSPARC T1 and UltraSPARC T2, has GNU General Public license [7].

## 1.1.2 RISC-V

RISC-V is an open-source, ISA (instruction set architecture) designed for high performance with great power efficiency which was created eight years ago at the University of California, Berkeley [8]. RISC-V is the fifth generation of the "reduced instruction set computer" type of architecture. What makes the "RISCV" architecture unique is not a great performance or technology. What makes this architecture unique is that it is completely redundant and therefore gives great promise to developers in terms of time and economy. RISC-V ISA delivers a new level of free open source which extensible hardware freedom on architecture, which makes this ISA innovative and futuristic. In addition, this ISA has many software tools, simulation tools, compiler tools, bootloaders, kenrels, OSs and debug tools avaible by the RISC-V foundation. Because of all these features, many developers and companies have created many cores created by using RISC-V. Some of these cores are shown in the Table 1.1 and some other SoCs are shown in Table 1.2.

| Name                                    | Links          | Priv.<br>spec  | User<br>spec        | License                                          | Maintainers                             |  |

|-----------------------------------------|----------------|----------------|---------------------|--------------------------------------------------|-----------------------------------------|--|

| rocket                                  | GitHub         | 1.11-<br>draft | 2.3-draft           | BSD                                              | SiFive, UCB Bar                         |  |

| freedom                                 | GitHub         | 1.11-<br>draft | 2.3-draft           | BSD                                              | SiFive                                  |  |

| Berkeley Out-of-Order<br>Machine (BOOM) | GitHub         | 1.11-<br>draft | 2.3-draft           | BSD                                              | Esperanto, UCB<br>Bar                   |  |

| ORCA                                    | GitHub         |                | RV32IM              | BSD                                              | VectorBlox                              |  |

| RI5CY                                   | GitHub         |                | RV32IMC             | RV32IMC Solderpad<br>Hardware<br>License v. 0.51 |                                         |  |

| Zero-riscy                              | GitHub         |                | RV32IMC             | Solderpad<br>Hardware<br>License v. 0.51         | ETH Zurich,<br>Università di<br>Bologna |  |

| Ariane                                  | Website,GitHub |                | RV64IMC             | Solderpad<br>Hardware<br>License v. 0.51         | ETH Zurich,<br>Università di<br>Bologna |  |

| Riscy Processors                        | Website,GitHub |                |                     | MIT                                              | MIT CSAIL CSG                           |  |

| OPenV/mriscv                            | GitHub         |                | RV32I(?)            | MIT                                              | OnChipUIS                               |  |

| VexRiscv                                | GitHub         |                | RV32I[M][C]         | MIT                                              | SpinalHDL                               |  |

| Roa Logic RV12                          | GitHub         | 1.9.1          | 2.1                 | Non-<br>Commercial<br>License                    | Roa Logic                               |  |

| SCR1                                    | GitHub         | 1.10           | 2.2,<br>RV32I/E[MC] | Solderpad<br>Hardware<br>License v. 0.51         | Syntacore                               |  |

| Hummingbird E200                        | GitHub         | 1.10           | 2.2,<br>RV32IMAC    | Apache 2.0                                       | Bob Hu                                  |  |

| Shakti                                  | Website,GitHub | 1.10           | 2.2,<br>RV64IMAFD   | BSD                                              | IIT Madras                              |  |

| ReonV                                   | GitHub         |                |                     | GPL v3                                           |                                         |  |

| PicoRV32                                | GitHub         |                | RV32I/E[MC]         | ISC                                              | Clifford Wolf                           |  |

| MR1                                     | GitHub         |                | RV32I               | Unlicense                                        | Tom Verbeure                            |  |

Table 1.1 : Some cores that used RISC-V ISA [2]

| Name           | Links            | Core                          | License                               | Maintainers                                 |  |  |

|----------------|------------------|-------------------------------|---------------------------------------|---------------------------------------------|--|--|

| Rocket<br>Chip | GitHub,Simulator | Rocket                        | BSD                                   | SiFive, UCB BAR                             |  |  |

| LowRISC        | GitHub           | RV32IM                        | BSD                                   | LowRISC CIC                                 |  |  |

| PULPino        | Website,GitHub   | RI5CY, Zero-<br>riscy, Ariane | Solderpad Hardware<br>License v. 0.51 | ETH Zurich, Università di<br>Bologna        |  |  |

| PULPissimo     | Website,GitHub   | RI5CY, Zero-<br>riscy, Ariane | Solderpad Hardware<br>License v. 0.51 | ETH Zurich, Università di<br>Bologna        |  |  |

| Briey          | GitHub           | VexRiscv                      | MIT                                   | SpinalHDL                                   |  |  |

| Riscy          | GitHub           | RV64I                         | MIT                                   | AleksandarKostovic                          |  |  |

| Raven          | GitHub           | PicoRV32                      | ISC                                   | RTimothyEdwards,<br>mkkassem (efabless.com) |  |  |

| PicoSoC        | GitHub           | PicoRV32                      | ISC                                   | Clifford Wolf                               |  |  |

| Icicle         | GitHub           | RV32I                         | ISC                                   | Graham Edgecombe                            |  |  |

Table 1.2 : Some SoCs that used RISC-V ISA [2]

In this project, LowRIS SoC (System on chip) is used which shown in Table 1.2. Some basic RISC-V instructions are similar to old RISC ISA's like OpenRISC some of them are shown in Table 1.3

| 31   | 27 | 26 22       | 21 17     | 16              | 12          | $11 \ 10$     | 9    | 7    | 6    | 0               |                   |

|------|----|-------------|-----------|-----------------|-------------|---------------|------|------|------|-----------------|-------------------|

|      |    | jump target |           |                 |             |               |      | opco |      | J-type          |                   |

| rd   | -  |             |           | upper immediate |             |               |      |      | opco |                 | U-type            |

| re   | -  | rs1         | imm[11:7] |                 | imm[6:0] fu |               |      |      | opco |                 | I-type            |

| imm[ |    | rs1         | rs2       |                 | imm[6:      |               | fune | ct3  | opco |                 | B-type            |

| rd   | -  | rs1         | rs2       |                 |             | nct10         |      |      | opco |                 | R-type            |

| rd   | ł  | rs1         | rs2       |                 | rs3         | fu            | nct5 |      | opco | ode             | R4-type           |

|      |    |             |           |                 |             |               |      |      |      |                 |                   |

|      |    |             | imm       |                 |             |               |      |      | 1101 | -               | J imm25           |

|      |    |             | imm       | 25              |             |               |      |      | 1101 |                 | JAL imm25         |

| imm  |    | rs1         | rs2       |                 | imm12       |               | 00   |      | 1100 |                 | BEQ rs1,rs2,imm12 |

| imm  |    | rs1         | rs2       |                 | imm12       |               | 00   |      | 1100 |                 | BNE rs1,rs2,imm12 |

| imm  |    | rs1         | rs2       |                 | imm12       |               | 10   |      | 1100 |                 | BLT rs1,rs2,imm12 |

| imm1 |    | rs1         | rs2       |                 | imm12       | o             | 10   |      | 1100 |                 | BGE rs1,rs2,imm12 |

| rd   | -  | rs1         |           | imm             |             |               | 00   |      | 0000 | -               | LB rd,rs1,imm12   |

| rd   | -  | rs1         |           | imm             |             |               | 00   |      | 0000 |                 | LH rd,rs1,imm12   |

| rd   |    | rs1         |           | imm             |             |               | 01   | -    | 0000 | -               | LW rd,rs1,imm12   |

| imm  |    | rs1         | rs2       |                 | imm12       |               | 00   |      | 0100 | -               | SB rs1,rs2,imm12  |

| imm  |    | rs1         | rs2       |                 | imm12lo     |               |      | 1    | 0100 |                 | SH rs1,rs2,imm12  |

| imm  |    | rs1         | rs2       |                 | imm12       | o             | 01   | -    | 0100 | -               | SW rs1,rs2,imm12  |

| rd   | -  | rs1         |           | imm             | imm12       |               |      | 0    | 0010 |                 | ADDI rd,rs1,imm12 |

| rd   |    | rs1         | 000000    |                 | shamt       |               |      | 1    | 0010 |                 | SLLI rd,rs1,shamt |

| rd   | ł  | rs1         |           | imn             | 112         |               | 01   | 0    | 0010 | 011             | SLTI rd,rs1,imm12 |

| rd   | 1  | rs1         |           | imn             | 112         |               | 10   |      | 0010 |                 | XORI rd,rs1,imm12 |

| rd   | -  | rs1         | 000000    |                 | sha         | $\mathbf{mt}$ | 10   |      | 0010 | -               | SRLI rd,rs1,shamt |

| rd   |    | rs1         | 000001    |                 | sha         | mt            | 10   |      | 0010 |                 | SRAI rd,rs1,shamt |

| rd   | -  | rs1         |           | imm             |             |               | 11   |      | 0010 |                 | ORI rd,rs1,imm12  |

| rd   | 1  | rs1         |           | imm             | imm12       |               |      | 1    | 0010 | 011             | ANDI rd,rs1,imm12 |

| rd   | 1  | rs1         | rs2       | 0000000         |             |               | 00   |      | 0110 |                 | ADD rd,rs1,rs2    |

| rd   |    | rs1         | rs2       | 1000000         |             |               | 00   |      | 0110 |                 | SUB rd,rs1,rs2    |

| rd   | -  | rs1         | rs2       | 0000000         |             |               | 00   |      | 0110 | ~ ~ ~           | SLL rd,rs1,rs2    |

| rd   |    | rs1         | rs2       |                 | 0000000     |               | 01   |      | 0110 |                 | SLT rd,rs1,rs2    |

| rd   | 1  | rs1         | rs2       | 0000000         |             | 01            | 1    | 0110 | 011  | SLTU rd,rs1,rs2 |                   |

| rd   | 1  | rs1         | rs2       |                 | 0000000     |               | 10   |      | 0110 |                 | XOR rd,rs1,rs2    |

| rd   | 1  | rs1         | rs2       |                 | 0000000     |               | 10   | 1    | 0110 | 011             | SRL rd,rs1,rs2    |

| rd   |    | rs1         | rs2       |                 | 1000000     |               |      | 1    | 0110 |                 | SRA rd,rs1,rs2    |

| rd   | l  | rs1         | rs2       |                 | 0000000     |               |      | 0    | 0110 | 011             | OR rd,rs1,rs2     |

| rd   | l  | rs1         | rs2       |                 | 0000000     |               |      | 1    | 0110 | 011             | AND rd,rs1,rs2    |

Table 1.3 : Some basic RISC instructions [9].

#### 1.1.2.1 RISC-V compiling tools

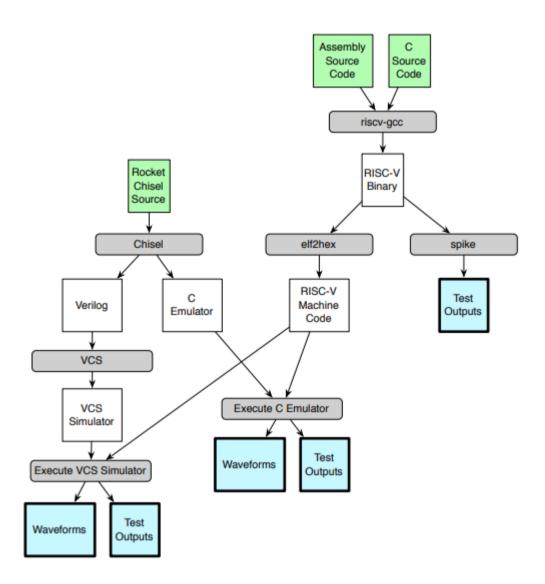

RISC-V has a standart toolchain like other devices which is GNU cross compiler toolchain. It just reimplemented for RISC-V ISA. Compiling flow just like normal GCC tools except it produce a unique binary for RISC-V ISA. However in this project, lowRISV SoC is used. So this part is not applied on project because of these tools are for standalone RISC-V cores. LowRISC also using this GCC tools but with different terminal commands. Toolchain usage diagram shown in Figure 1.1 for general flow map.

Figure 1.1: RISC-V GCC toolflow. Greens are input files and blues are output files [9].

This is just a standalone RISC-V coding toolflow. In our project, RISC-V core will run our applications on a Linux OS and will execute C language commands.

#### 1.1.3 LowRISC

LowRISC an organisation that creating its own unique open sourced SoC based on 64 bit RISC-V ISA. This SoC is capable of running on a debian Linux OS. Organisation also working closely with University of Cambridge and with a community that aims to improve this SoC in terms of hardware and software design [1]. The LowRISC team is developing the system for the sake of three main objectives.

• Their designs are licensed and developed as allowed together with codevelopers from many parts of the world. Free and open RISC-V ISA is being implemented. Thus, a common open-source SoC will be completely standardized.

- The advantage of being open source is that it is a fully auditable system and it is aimed at being as safe as it is economically by using technologies tagged memory.

- By trying to reflect the flexibility and diversity of the software to the hardware, to develop a future SoC by creating a system that can be improved in real-time applications.

Rocket-Chip Rocket Rocket Rocket lowRISC-Chip Core Core Core TileLink AXI L1 \$ L1 \$ L1 \$ Debug network RTC Chisel modules Verilog modules WOR dge Tag storage TileLink TileLink IO network MEM network L2 \$ L2 \$ Keyboard Screen Mem BootROM (devicetree) Access tag cache Buffer Minion Subsystem AXI IO network (PULPino) AXI mem network System control SPI DDR UART BRAM SD Card GPIOs Flash Host

A high level top view of lowRISC chip can be seen in Figure 1.2.

Figure 1.2 : Top view of lowRISC SoC [10]

However, version of lowRISC chip used in this project is 0.6 which does not include minion subsystem. Reason is that running Linux with that core makes Linux slow. In future releases it will come again. But still we can use SD Card, vga screen, ps2 keyboard. And also L2 caches removed from this version with upgrade of new version of TileLink network [11].

## 1.1.3.1 Rocket-Core view

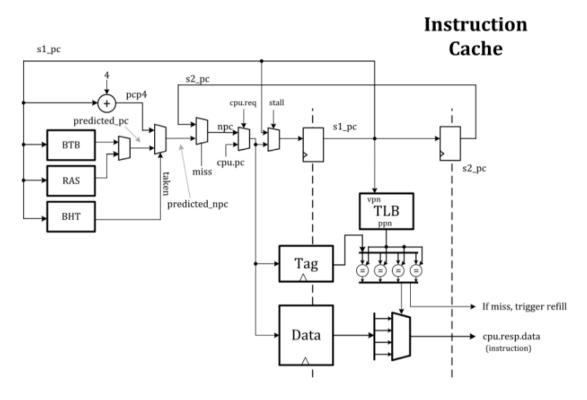

Rocket core contains a 5-stage pipeline and is built on RISCV64G, which includes one integer ALU and one optional FPU. In some aspects it is called 6-stage pipeline

because of "pcgen" stage is included with it. But lowRISC team differs this stage like a standalone stage. Pcgen and fetch stages are shown in Figure 1.3.

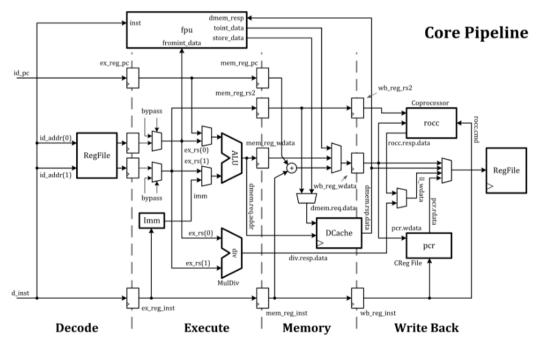

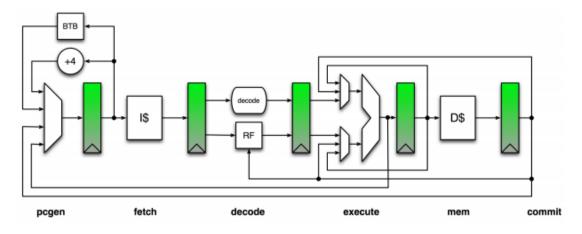

Figure 1.3 : Instruction cache which includes pcgen and fetch stages [12]. Remained stages are shown in Figure 1.4.

Figure 1.4 : Other stages of pipeline [12].

General pipeline diagram can be shown in Figure 1.5.

Figure 1.5 : All pipeline stages in one diagram [9].

L1 data cache is in Figure 1.6.

Figure 1.6 : L1 data cache overview [12].

And all architecture of Rocket Core in Figure 1.7.

Figure 1.7 : General microarchitecture of all system [9].

#### 1.1.4 Image processing and filters

Image processing can be defined by extracting features to be used from any camera image, video image, or image, and making a result by using these features after rendering the computer to process [13]. Images can be considered mathematically twodimensional arrays in digital media. On top of that, the signal processing algorithms can be processed just like a normal analog signal. For this reason, it has an important place in today's machine learning algorithms and many computer science. Today, in our world, from the medicine to the automotive sector, military and scientific research has a very important importance. This recent importance of image processing also plays an important role in what this project is working on. Although the algorithms are tried to be optimized by software, the importance of hardware comes to the fore as well. For these algorithms, many companies are very stable in designing their own equipment and transferring cost, time and labor to these designs. For this reason, it is appropriate to use the lowRISC project, which is open source in this graduation project, for image processing. A general flow for image processing algorith can be shown in Figure 1.8.

Figure 1.8 : Image processing algorithm general flow [14].

#### 1.1.4.1 Kernel

In image processing, the kernel can be defined as a square mask or convolution matrix, which multiplies certain pixels in the image with their weights and add these weighted pixels with each other and creates new pixels of the resulting image.

#### 1.1.4.2 Convolution operation

Convolution operation is generally can be described as any pixel in an image will be additioned with pixels in the neighbor of central pixel values which multiplied by the kernel weights of each pixels, and every pixel in the picture sees this process in sequence. Briefly, it is an arithmetic that allows the new picture to be formed by sliding the kernel on to image from left to right and from top to bottom. Process can be shown in Figure 1.9.

Figure 1.9 : Convolution operation.

#### 1.1.5 General flow of project

The overall flow of the project will be covered under this heading. Each step written here will be explained in detail in the next chapter. What we need first is a computer and an external or internal disk for installing the Ubuntu operating system. Then, to run the lowRISC chip in the FPGA, the Vivado program of Xilinx will be installed. There may also need a monitor to connect the FPGA to the monitor, especially in terms of visual comfort. There is also a need for an ethernet cable for remote communication

with the lowRISC Soc in the FPGA. A minimum of 4 GB (16 GB recomended) SD card and a pc compatible card reader requires to install linux and some applications. Other option is connecting and using a keyboard through USB interface of FPGA and executes commands from there. Once the Ubuntu disk has been installed, the necessary software programs for the compilation of lowRISC and the execution of the software will be installed and some variables will be defined in the operating system. After this step, the compiled software and hardware files will be thrown into the FPGA and the lowRISC will be running. The format of the image to be processed will be changed for processing with C. The C codes of the image processing algorithm and the image to be processed will be transferred to the lowRISC SoC using the SSH protocol. The algorithms will be run on the lowRISC and the resulting image will be transferred to the host computer using the SSH protocol to be monitored again.

#### 1.2 Literature Review

#### 1.2.1 Literature review at Istanbul Technical University

• (Güngör, Öndeş, Sarı, Uçkun; 2018) "Instruction Set Extension Of Some Processors For Secure Iot Implementations"

The main subject of this thesis is using AES and PRESENT cryptology algoritms with instartcion set extention (ISE) in open source processors and to increase the security of these processors for IoT applications. One of the core of the project is the Pulpino RI5CY which belongs to the ETH Zurich. The developer Talip Tolga Sarı first placed this core on the Nexys4 DDR development board which belongs to Xilinx and then observed that it was working by testing. After this stage, the main subject of the thesis AES application was implemented by using the instruction set extention method, successfully performed [15].

#### **1.2.2 Literature review at Turkey**

So far, no thesis work about this subject has been done in our country yet. However, one of Turkey's largest defense industrial firm ASELSAN is a member of RISC-V organisation ranked as silver member.

#### 1.2.3 Global Literature review

• (T. Liu, G. Shi, L. Chen, F. Zhang, Y. Yang and J. Zhang; 2018) "TMDFI: Tagged Memory Assisted for Fine-Grained Data-Flow Integrity Towards Embedded Systems Against Software Exploitation"

Modern software attacks often benefit from problems caused by memory corruption. While the classical data flow integrity provides a good solution to these problems, they have a large impact on the speed of the applied system and create time problems because of origin of this algorithm is software based. For all these reasons, a new data stream integrity hardware, which supports the tagged memory system, is presented by the developers. In particular, the hardware prototype has been tested on the lowRISC with the RISCV-based core and major improvements in speed and time have been observed. According to the results, the data flow integrity hardware system in the real-time tests reduced the pressure of system from 104% to 39%, the space overhead shrinks from 50% to 12.5% [16].

# • (A. Ramos, A. Ullah, P. Reviriego and J. A. Maestro; 2018) "Efficient Protection of the Register File in Soft-Processors Implemented on Xilinx FPGAs"

The main reason for this study is that software processors are designed on FPGA by using SRAM and also the register structure is one of the most critical information carrier elements for a processor. Regarding external factors, especially in the aviation and space sectors, the register values in the processors can be changed and data losses or errors are experienced. In this study, error tolerance system has been tried to be applied to register file. This system is used to add the register file to the memory element in the processor. The RISCV-based LowRISC SoC was used for testing. A parity based error finder and interchangeable logic system designed to eliminate single-bit errors. As a result, the designed system not only saves the faulty bits but also occupies much less space than the general "Triple Modular Redundancy" module [17].

## 2. IMPLEMENTING LowRISC PROCESSOR ON AN FPGA

#### 2.1 Gathering Required Environment

First, the "Ubuntu 16.04.5 LTS" [18] operating system must be installed on an external or internal disk. A second method, the virtual machine method, has also been tried, but the use of virtual machines is not recommended because of some tools and hardware constraints [19].

Immediately after this process, it is necessary to install Vivado 2018.1 [20], which is owned by Xilinx and is required to place lowRISC in FPGA. In installation tab you must use WebPackedition of Vivado. It is also important that 2018.1 must be installed for the lowRISC v0.6. Because in feature releases of Vivado some IP Cores would change. This will create a conflict while creating lowRISC Vivado project After installation fallowing command must be entered at bottom of .bashrc file in your home directory.

#### • source /opt/Xilinx/Vivado/2018.1/settings64.sh

After enterence of that command start a new terminal and write Vivado. If program is starting than everything is until now is okey.

#### 2.1.1 Installation of cable drivers

Installation of Vivado on Ubuntu needs also cable driver setup. If these drivers are not installed, Vivado program does not recognise FPGA board on bitstream process. Fallowing driver packages are delivered from Digilent. These are recommended drivers for board [19].

- Adept 2.16.1 Runtime, X64 DEB

- Adept 2.2.1 Utilities, X64 DEB

Drivers can be downloaded from Digilent's website [21]. After downloading them, do not forget to install these drivers.

After these driver installation JTAG driver also must be installed. Open a fresh terminal and enter fallowing codes.

- cd/opt/Xilinx/Vivado/2018.1/data/xicom/cable\_drivers/lin64/install\_script/install\_drivers

- *sudo sh install\_digilent.sh*

Now everything is set and ready to next installations.

## 2.1.2 Installation of Cmake

Cmake [22] must be installed to compile some sowftwares for lowRISC. To install cmake linux version 3.13.2, it can be downloaded from <u>https://cmake.org/download/</u> [22]. After downloading the files, the commands below must be entered inside the download folder to the terminal

- ./bootstrap

- make

- make install

## 2.1.3 Downloading LowRISC chip git repository

This repository contains all software and toolchains including with all LowRISC files. Before downloading this repo make sure all packages are updated. Following command update all packages [23].

sudo apt-get install autoconf automake autotools-dev curl \ libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison \ flex texinfo gperf libncurses5-dev libusb-1.0-0-dev libboost-dev \swig git libtool libreadline-dev libelf-dev python-dev \microcomchrpath gawk texinfo nfs-kernel-server xinetd pseudo \ libusb-1.0-0-dev hugo device-tree-compiler zlib1g-dev libssl-dev \ debootstrap debian-ports-archive-keyring qemu-user-static iverilog \ openjdk-8-jdk-headless iperf3 libglib2.0-dev libpixman-1-dev

After these commands make sure Ubuntu has git. Git also can be installed with fallowing command;

• sudo apt-get install git

With proper installation of git, now lowRISC v0.6 could be downloaded from git repo. Following command must entered in work directory. In my case it is in /home/user/vivado/.

• git clone -b refresh-v0.6 --recursive https://github.com/lowrisc/lowrisc-chip.git lowrisc-chip-refresh-v0.6 cd lowrisc-chip-refresh-v0.6

When entering "lowrisc-chip-refresh-v0.6" directory, some main directories can be seen. Their purposes and usages are listed below [23];

- **fpga:** FPGA demo implementations

- o board: Demo projects for individual development boards.

- nexys4: Files for the Nexys<sup>TM</sup>4 DDR Artix-7 FPGA Board.

- debian-riscv64: Scripts to bootstrap a Debian Linux RISCV system

- riscv-linux: The Linux RISCV kernel with LowRISC device drivers

- rocket-chip: The Rocket core and its sub-systems.

- o firrtl: Hardware description intermediate language

- o hardfloat: Hardware floating-point arithmetic unit

- torture: Tricky tests that stress the CPU

- riscv-tools: The cross-compilation and simulation tool chain.

- riscv-fesvr: The front-end server that serves system calls on the host machine.

- riscv-gnu-toolchain: The GNU GCC cross-compiler for RISC-V ISA.

- riscv-isa-sim: The RISC-V ISA simulator Spike

- riscv-opcodes: The enumeration of all RISC-V opcodes executable by the Spike simulator.

- riscv-pk: The proxy kernel need for running legacy programs in the Spike simulator.

- **riscv-tests:** Tests for the Rocket core.

- src: The top level code of lowRISC chip.

- main: The Verilog code for hardware implementation.

- **test:** The Verilog/C++(DPI) test bench files

- qemu: User mode emulation of RISCV instruction set

### 2.1.4 Installing RISC-V GNU toolchain

Firstly, default gcc and g++ must be updated. Fallowing commands will work for it.

- sudo apt update

- sudo apt upgrade

- sudo apt install build-essential

Gcc version must be higher than 5.2.

- gcc-version

- which gcc

After these steps, Reopen "lowrisc-chip-refresh-v0.6" folder and open terminal at this folder.

- *cd*/*rocket-chip*/*riscv-tools*

- ./build.sh

This process is really takes a long time depending computer system. Like 30min- 2 hours. If everything is correct next step is updating .bashrc commands. Open new terminal at "lowrisc-chip-refresh-v0.6" folder

• ./set\_env.sh

At command window result of bash commands will seen in terminal screen. Copy all variables paste to .bsahrc file. Final version of .bashrc can be seen in Figure 2.1

```

source /opt/Xilinx/Vivado/2018.1/settings64.sh

```

```

export TOP=/home/bartu/Vivado/lowrisc-chip-refresh-v0.6

export RISCV=/home/bartu/Vivado/lowrisc-chip-refresh-

v0.6/riscv

export OSD ROOT=/home/bartu/Vivado/lowrisc-chip-refresh-

v0.6/tools

export PYTHONPATH=/home/bartu/Vivado/lowrisc-chip-refresh-

v0.6/tools/lib/python2.7/site-packages:

export PATH=/home/bartu/Vivado/lowrisc-chip-refresh-

v0.6/tools/bin:/opt/Xilinx/SDK/2018.1/bin:/opt/Xilinx/SDK/2018

.1/qnu/microblaze/lin/bin:/opt/Xilinx/SDK/2018.1/qnu/arm/lin/b

in:/opt/Xilinx/SDK/2018.1/qnu/microblaze/linux toolchain/lin64

le/bin:/opt/Xilinx/SDK/2018.1/gnu/aarch32/lin/gcc-arm-linux-

gnueabi/bin:/opt/Xilinx/SDK/2018.1/gnu/aarch32/lin/gcc-arm-

none-eabi/bin:/opt/Xilinx/SDK/2018.1/gnu/aarch64/lin/aarch64-

linux/bin:/opt/Xilinx/SDK/2018.1/gnu/aarch64/lin/aarch64-

none/bin:/opt/Xilinx/SDK/2018.1/gnu/armr5/lin/gcc-arm-none-

eabi/bin:/opt/Xilinx/SDK/2018.1/tps/lnx64/cmake-3.3.2/bin:/opt

/Xilinx/DocNav:/opt/Xilinx/Vivado/2018.1/bin:/home/bartu/bin:/

home/bartu/.local/bin:/usr/local/sbin:/usr/local/bin:/usr/sbin

:/usr/bin:/sbin:/bin:/usr/games:/usr/local/games:/snap/bin:/ho

me/bartu/Vivado/lowrisc-chip-refresh-v0.6/riscv/bin

export LD LIBRARY PATH=/home/bartu/Vivado/lowrisc-chip-

refresh-v0.6/tools/lib:/home/bartu/Vivado/lowrisc-chip-

refresh-v0.6/riscv/lib

export PKG_CONFIG_PATH=/home/bartu/Vivado/lowrisc-chip-

refresh-v0.6/tools/lib/pkgconfig

export FPGA BOARD=nexys4 ddr

```

### Figure 2.1 : Bashrc commad window.

If getting response for fallowing command, toolchain has successfully installed.

• which riscv64-unknown-elf-gcc

# 2.2 Installing Linux to lowRISC

From now there are two ways to get Linux to lowRISC, first one is create your own Linux kernel from tools or, get binary release from lowRISC tutorial page [24]. Creation new Kernel is a more complex way and making mistakes at this stage is really critical. For now it is safe choğice to getting binary release and continue on uploading Linux lowRISC. detailed guide could system to А be seen on https://www.lowrisc.org/docs/download-install-debian/ to continue on building own Kernel [19].

To install binary release input fallowing codes to terminal

• git clone <u>https://github.com/lowRISC/lowrisc-quickstart.git</u>

- cd lowrisc-quickstart

- make getrelease

After these commands three important files will be appear in directory [24].

- **boot.bin** includes Linux kernel, Berkeley bootloader, and initial ramdisk.

- **chip\_top.bit** The FPGA bitstream containing the lowRISC SoC which includes RISCV processor and peripherals and the first-stage booter

- **rootfs.tar.xz** The compressed tape archive containing the Debian root filing system for RISCV

After that process insert your SD card to card reader and to your computer. After recognized from your Ubuntu, type lsblk command to your command window too see all storage devices listed on your computer. It is really dangerous that choosing right name on that list. If wrong choice has choosen, own PC data could be formatted without any chechkpoint. In Figure 2.2 a default 16 GB SD Card shwon at lsblk list.

| \$ lsblk              |         |    |        |    |      |            |                |

|-----------------------|---------|----|--------|----|------|------------|----------------|

| NAME                  | MAJ:MIN | RM | SIZE   | R0 | TYPE | MOUNTPOINT |                |

| sda                   | 8:0     | 0  | 931.5G | 0  | disk |            |                |

| —sdal                 | 8:1     | 0  | 243M   | 0  | part | /boot      |                |

| —sda2                 | 8:2     | 0  | 1K     | 0  | part |            |                |

| —sda5                 | 8:5     | 0  | 931.3G | Θ  | part |            | 1.27           |

| —ubuntu-root (dm-0)   | 252:0   | 0  | 923.4G | Θ  | lvm  | 1          |                |

| └ubuntu-swap 1 (dm-1) | 252:1   | 0  | 7.9G   | Θ  | lvm  | [SWAP]     |                |

| sdb                   | 8:16    | 1  | 14.9G  | Θ  | disk | K          |                |

| —sdb1                 | 8:17    | 1  | 56M    | Θ  | part | /media/    | /boot          |

| —sdb2                 | 8:18    | 1  | 3G     | 0  | part | /media/    | /13d368bf-6dbf |

| sr0                   | 11:0    | 1  | 1024M  | 0  | rom  |            |                |

| \$                    |         |    |        |    |      |            |                |

### Figure 2.2: 16 GB SD Card

A new fresh SD Card only been as sdx1 as 14.9 GB strorage. Check twice SD Card device name and never forget! In fallowing commands name of device entered as sdx for copy paste safety. X letter must be changed with correct SD Card name.

• make umount USB=sdx

If SD card used before type instead:

• Make USB=sdx cleandisk partition

If any error occurs during these processes repeat all steps two steps above independently after reinserting SD Card to PC. After operations run lsblk to see results at Figure 2.3.

| sdc    | 8:32 | 1 | 14.9G | 0 disk |

|--------|------|---|-------|--------|

| -sdc1  | 8:33 | 1 | 32M   | 0 part |

| -sdc2  | 8:34 | 1 | 2G    | 0 part |

| -sdc3  | 8:35 | 1 | 512M  | 0 part |

| L-sdc4 | 8:36 | 1 | 12.3G | 0 part |

Figure 2.3 : After commands worked properly.

After that typing fallowing command will install all 3 files above proper locations to SD Card.

• make USB=sdx mkfs fatdisk extdisk

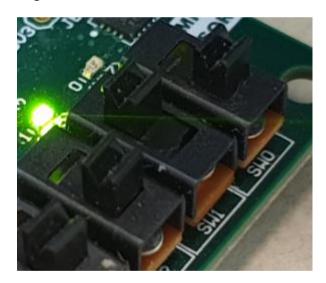

Say yes on terminal if asks any question. First question is asking to user create new file system for lowRISC. Second step asks for write permission of kernel and BBL to DOS partition. After all these steps now unplug SD Card from computer and Plug it to FPGA. Also on FPGA board JP1 must stand at QSPI mode and JP2 must stand at SD mode as shown in Figure 2.4 [24].

Figure 2.4 : Jumper positions to boot from SD card

From now its all set to boot lowRISC to FPGA. Fallowing code will install bitstream file to QSPI Flash.

• make program-cfgmem

After these process Vga screen connected to the FPGA seems like at Figure 2.5.

Figure 2.5 : Boot screen at VGA display.

And FPGA waits in waiting input mode at Figure 2.6.

Figure 2.6 : Waiting input mode.

In this step, we should choose boot from SD Card and making switch 1 high will do job which shown in Figure 2.7.

Figure 2.7 : Booting from SD card chosen

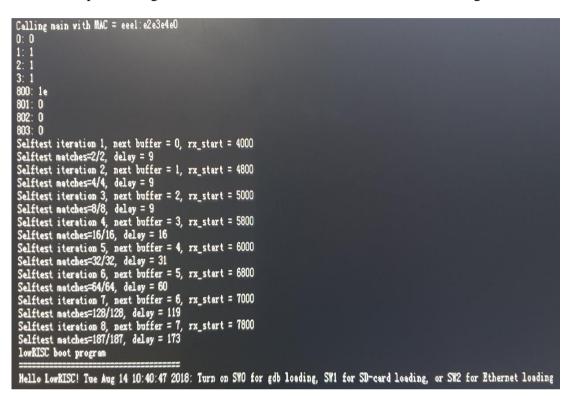

Choice must be done when before giving power FPGA. After restarting FPGA with choice which sw1 goes up, Figure 2.8, Figure 2.9 and 2.10 shows FPGA u-boot based operations.

Figure 2.8 : Successfully boot operation started.

Figure 2.9

```

lowRISC boot program

______

Hello LowRISC! Tue Aug 14 10:40:47 2018: Booting from FLASH because SW1 is high ...

```

#### Figure 2.10

Output of First stage bootloader in Figure 2.11. If it does not write "Bus Width : 4 bit" it means your SD card does not set properly [24].

| OEM: 5344<br>Name: SC16G<br>Bus Speed: 5000000<br>High Capacity: Yes<br>Capacity:<br>lu.ld GiB<br>Bus Width: 4-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 0: 33 c0 8e d0 bc 00 Tc 8e c0 8e d8 be 00 Tc bf 00 06 b9 00 02 fc f3 s4 50 68 1c 06 cb fb b9 04<br>20: bd be 07 80 Te 00 00 Tc 0b 0f 85 0e 01 83 c5 10 s2 f1 cd 18 88 56 00 55 c6 46 11 05 c6 46 10<br>40: b4 41 bb sa 55 cd 13 5d 72 0f 81 fb 55 sa 75 09 f7 c1 01 00 74 03 fe 46 10 66 60 80 Te 10 00<br>60: 25 66 68 00 00 00 00 66 ff 76 08 68 00 00 68 00 7c 68 01 00 68 10 00 b4 42 8a 56 00 8b f4 cd<br>80: 9f 83 c4 10 9e eb 14 b8 01 02 bb 00 7c 8a 56 00 8a 76 01 8a 4e 02 8a 6e 03 cd 13 66 61 73 1c<br>a0: 4e 11 75 0c 80 Te 00 80 0f 84 8a 00 b2 80 eb 84 55 32 e4 8a 56 00 cd 13 5d eb 9e 81 3e fe 7d 9<br>c0: aa 75 6e ff 76 00 e8 8d 00 75 17 fa b0 d1 e6 64 e8 83 00 b0 df e6 60 e8 7c 00 b0 ff e6 64 e8 7c<br>e0: 00 fb b8 00 bb cd 1a 66 23 c0 75 3b 66 81 fb 54 43 50 41 75 32 81 f9 02 01 72 2c 66 68 07 bb 0<br>100: 00 66 68 00 02 00 00 66 66 08 00 7c 00 00 cd 18 a0 b7 07 eb 08 a0 b6 07 eb 03 a0 b5 07 32 df<br>100: 00 66 68 00 02 00 00 66 66 08 00 7c 00 00 cd 18 a0 b7 07 eb 08 a0 b6 07 eb 03 a0 b5 07 32 df<br>120: 61 68 00 00 07 cd 1a 5a 32 ff ea 00 7c 00 00 cd 18 a0 b7 07 eb 08 a0 b6 07 eb 03 a0 b5 07 32 df<br>140: 05 00 07 8b f0 ac 3c 00 74 09 bb 07 00 b4 0e cd 10 eb f2 f4 eb fd 2b c9 e4 64 eb 00 24 02 e0 ff<br>180: 20 6c 6f 61 64 69 6e 67 20 73 79 73 74 69 6f 6e 20 74 61 62 6c 65 00 45 72 72 6f 77<br>1a0: 67 20 6f 70 65 72 61 74 69 6e 67 20 73 79 73 74 65 6d 00 00 00 63 7b 9a ef be ad de 00 00 80 00<br>1e0: 01 02 3f 1f 20 00 08 00 00 ff ff 00 00 00 00 00 01 21 83 3f 20 20 00 86 11 00 00 00 40 00 00 00<br>1e0: 01 21 82 3f a0 20 00 08 41 00 00 00 10 00 00 00 81 21 83 1f e0 59 00 08 51 00 00 c4 89 01 55 as | 00<br>74<br>13<br>55<br>55<br>75<br>0<br>66<br>66<br>88<br>2 |

Figure 2.11 : First stage bootloader output.

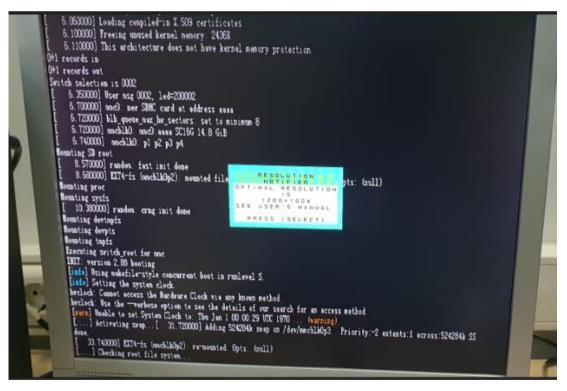

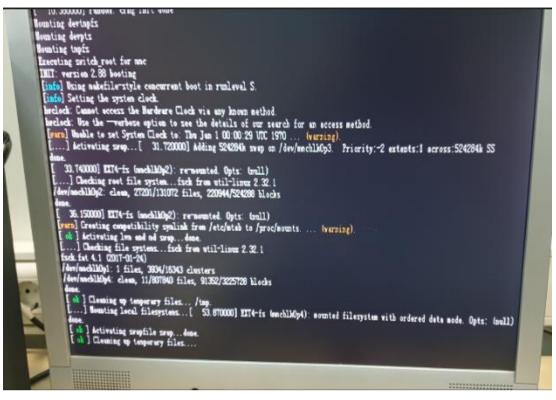

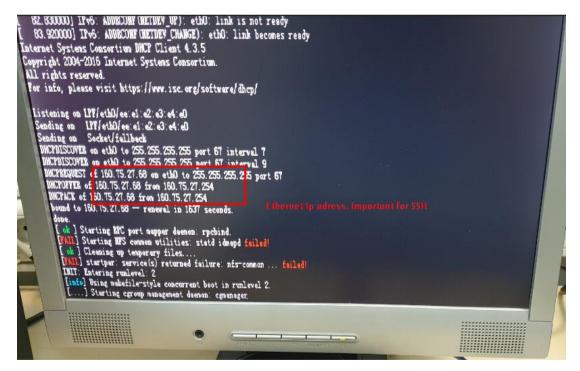

From now fallowing figures which are Figure 2.12, 2.13, 2.14, 2.15 are serial stages of booting Linux to lowRISC.

|                       |                                                                                                                                                   | ALLUSYNC LUD 479M |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                       | ***************************************                                                                                                           |                   |

|                       | ******                                                                                                                                            |                   |

|                       | CITCITITITY ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN ANALYMAN                                    |                   |

|                       | 111111111111111 ++++++++++++++++++++++                                                                                                            |                   |

|                       | IIIIIIIIIIIII ****************                                                                                                                    |                   |

| 100                   | IIIIIIIIIIIII TAAAAAAAAAAAAAAAAAAAAAAAA                                                                                                           |                   |

| 1000                  | IIIIIIIIIIIIII WWWWWWWWWWWWWWWWWWWWW                                                                                                              |                   |

| 1.00                  |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       | II 99999999999999999999999999999999999                                                                                                            |                   |

|                       | II WWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWW                                                                                                            |                   |

|                       | IIII WINNINNINNINNINNINNINNINNINNINNINNINNINN                                                                                                     |                   |

| / 1                   | IIIII WWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWW                                                                                                            |                   |

|                       | TITITI WYTYWYWYWYWYW TITITYT                                                                                                                      |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       |                                                                                                                                                   |                   |

|                       | INSTRUCTION SETS VANT TO BE FREE                                                                                                                  |                   |

| and the second second | "Louded 8055218 beter to namera allow 27000000 from boot bin of 8055208 beter                                                                     |                   |

|                       | -Level 2055278 Level to and 10 BC FARE<br>besh = 5542004858-850.5504705571.65158                                                                  |                   |

|                       |                                                                                                                                                   |                   |

|                       | Sections[0]: manager (20000000, 0x:071001000, 0x:07001000);<br>Sections[1]: manager (20000000, 0x:07000000, 0x:59);<br>manager (20000050, 0x:59); |                   |

|                       |                                                                                                                                                   |                   |

|                       | Section 21 memory (BY200000 0-02000000 n memory)                                                                                                  |                   |

|                       | Boot the loaded program                                                                                                                           |                   |

Figure 2.13 : There could be some warns. It will continue

Figure 2.14 : Other boot informations

Figure 2.15 : Ethernet connection is okey too.

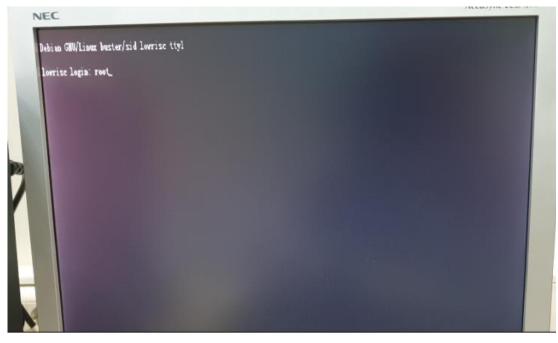

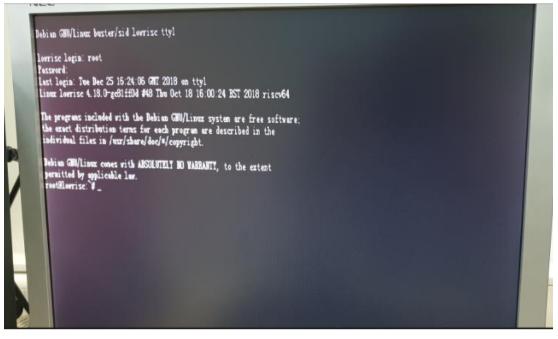

After these steps all boot operations are set and at the last screen user will see login screen like in Figure 2.16.

Figure 2.16 : Login screen and first login must be root.

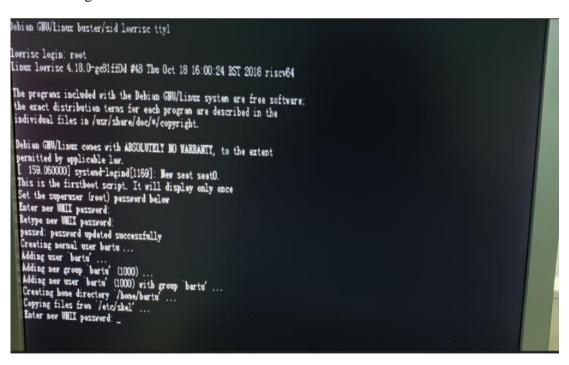

First login must be root and givin any root password key is okey to root. After that lowRISC will prompt user for superuser set then creates a normal user which is also has same name of your Ubuntu computer name. In my example it is *bartu*. Also a password key must be entered to that user. Same password with root will work which shown in Figure 2.17.

Figure 2.17 : Login screen with prompts.

After all these setups, now lowRISC will ask user name and password key to login machine. After entering either root or Ubuntu user, a bash command screen will appear at VGA display which shown in Figure 2.18.

Figure 2.18 : Bash command screen.

From now, there is 2 way to use lowRISC. First way is using your Ubuntu machine and connect and control lowRISC with SSH protocol. Other is directly with PS2 FPGA keyboard and VGA monitor. It is recommanded that updating or installing any program to lowRISC must be from FPGA keyboard. SSH protocol gives shows some problems and errors at this stage.

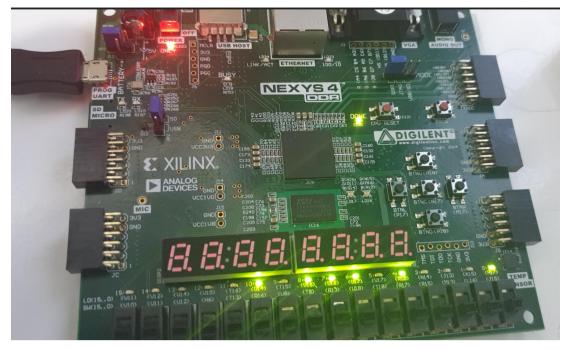

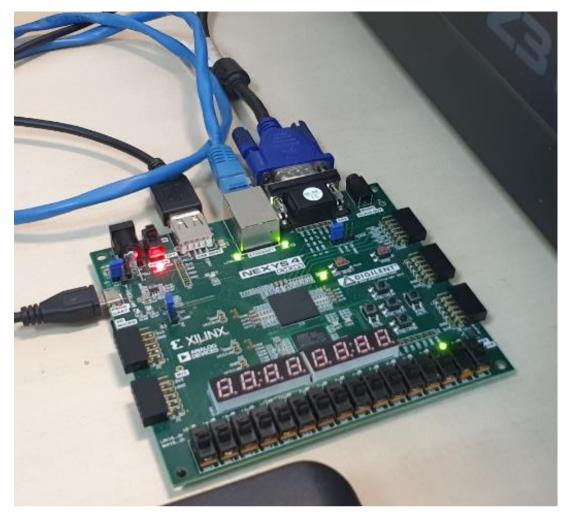

# 2.3 Peripherals of system

LowRISC 0.6 version has some good peripherals to use system like standalone PC. One is a ps2 – USB connection keyboard which is easy to use lowRISC with bash commands. Second peripheral is ethernet cable support. This allows lowRISC to connect internet and get some new apps for ported RISCV architecture. These app list and app repository can be <u>shown at this page</u> [25]. And last peripheral is VGA display port. LowRISC team makes this VGA display as a text display which only encodes and writes some character with support of color. So if user want to show picture from lowRISC to VGA display for now it is not possible to do. Figure 2.19 shows all connected peripherals to FPGA.

Figure 2.19 : Full peripheral connection.

# 2.4 Implementing image filter algorithms to lowRISC

Since package support for RISCV is limited for now, I decided to use pure C language to image filtering and processing operations. But the great constraint is pure C which has no additional library is not able to common image formats. For this purpose a little research shows us there is some formats even pure C could read an image and write a output image file. Project chose to use .ppm file.

# 2.4.1 PPM format

This format is a lowest common denominator color image format. Format is so inefficient in terms of compressing and image quality. Also format does not include really little information about file. What makes this format good is format makes any image read easy and makes easy to process data of image which is essential for our system. Format in Hex reader shown at this format:

- A "magic number" that gives file type, which is "P6" for ppm.

- CR ASCII.

- Width information as ASCII.

- Whitespace.

- Height information as ASCII.

- CR ASCII.

- Maximum color value of a pixel. General maximum 255 and minimum 0 in ASCII format.

- CR ASCII.

- And image vector values in ASCII format. Image starts From left to right and Upper Line is first line to start writing. There is no whitespace characters between pixels and rgb values. First value is Red of pixel 1, second is Green of pixel 1, third is blue of pixel 1 and after that goes pixel 2 rgb values and so on.

### 2.4.2 Converting PNG to PPM

Since ppm format is not common as like jpeg or png, input image firtly must converted on ppm from png. However for now there is no converter for lowRISC system, we should convert it at Ubuntu machine and after that give ppm image to lowRISC as input image. For this purpose a program named ImageMagick msut be installed on Ubuntu. To install enter fallowing code:

- sudo apt-get install imagemagick

- sudo apt-get install gcc php-common

- sudo apt-get install php-imagick

- service apache2 restart