# Accurate active-feedback CMOS cascode current mirror with improved output swing

## ALI ZEKI† and HAKAN KUNTMAN†

An improved active-feedback CMOS cascode current mirror is introduced which has a very accurate current reflection ratio, while achieving the same output impedance as that of an equivalent conventional active-feedback cascode current mirror (CAFCCM) and a wider and optimal output dynamic range. The design can be made with even lower power consumption than CAFCCM and similar chip area. The technique can also be implemented in bipolar and BiCMOS integrated circuit design. The new structure does not need an additional constant current source as CAFCCM does. With these features, the circuit is suitable for use in high precision analogue integrated circuit design; especially in design of currentmode and low-voltage integrated circuits.

## 1. Introduction

Current mirrors are very important for analogue integrated circuits because of their wide use as constant current sources or active loads in amplifier stages. Their importance is increasing continuously due to the developments in current-mode integrated circuit design. Output impedance, current reflection (or transfer) accuracy and output swing are important parameters.

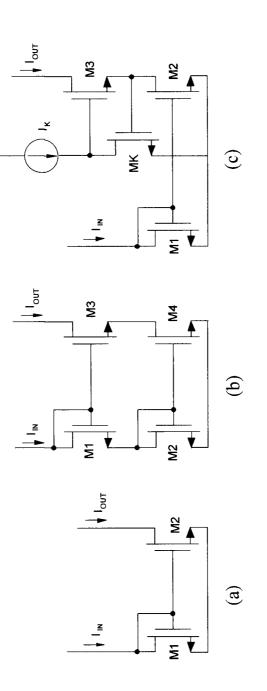

Classical cascode current mirror (Fig. 1(b)) achieves a larger output impedance and a higher transfer accuracy with respect to a simple current mirror (Fig. 1(a)) but the output voltage swing gets worse. Furthermore, the input voltage swing of the current mirror is worsened, which may be a problem if the input current is not fixed, as in the current mirrors of an OTA (Zeki and Kuntman 1996). The active-feedback cascode stage (Säckinger and Guggenbühl 1990) can be utilized to build the conventional active-feedback cascode current mirror (CAFCCM) of Fig. 1 (c) which achieves a much larger output impedance and a relatively wider output voltage swing than those of the classical cascode current mirror, while keeping the same input voltage swing as that of the simple current mirror (Yang and Allstot 1990). High output impedance is achieved by the active negative feedback through the amplifier stage  $I_K-M_K$  and the source follower  $M_3$ . The most important disadvantage is that  $V_{DS2} = V_{GSK}$  is determined by  $I_K$  and  $M_K$ ; therefore for  $I_{OUT} = I_{IN}$  to be accurately achieved,  $I_K$  and  $M_K$  must be chosen such that  $V_{DS2} = V_{GS2}$  is satisfied; otherwise transfer accuracy is rather lower than that of a classical cascode current mirror, due to the channel length modulation effect (Zeki and Kuntman 1995). This transfer error gives rise to off-set and nonlinearity problems in analogue circuits (Palmisano et al. 1995). On the other hand, if the input current I<sub>IN</sub> is not fixed, then two problems arise:

(a)  $V_{\text{DS2}} = V_{\text{GS2}}$  cannot be achieved, except in a single case (i.e. when  $V_{\text{GSK}} = V_{\text{GS1}}$ ), degrading transfer accuracy.

0020-7217/98 \$12.00 C1998 Taylor & Francis Ltd.

Received 30 October 1996; accepted 7 July 1997.

<sup>†</sup> İstanbul Technical University, Faculty of Electrical and Electronics Engineering, Department of Electronics and Communication Engineering, 80626, Maslak, İstanbul, Turkey. Tel: +90 212 285 36 44; Fax: +90 212 285 36 79; E-mail: alizeki@ehb.itu.edu.tr.

(b) If  $I_{IN}$  (thus  $V_{GS2}$ ) is large enough to drive  $M_2$  into the triode region (because of fixed  $V_{DS2}$ ), then the current mirror does not operate properly.

However, if  $V_{DS2}$  can always be adjusted to be equal to  $V_{GS2}$ , these problems are overcome optimally. Then, output swing is not fixed but dependent on  $V_{GS1}$  (thus, on  $I_{IN}$ ). This dependency makes it possible to achieve an optimal output swing for every  $I_{IN}$  value, while keeping the high current transfer accuracy. Note that,  $V_{DS}$ dependency of  $I_D$  is not too strong for a MOSFET operating in saturation; therefore, to achieve an accurate current reflection ratio,  $V_{DS2} = V_{DS1}$  equality need not be precisely satisfied.

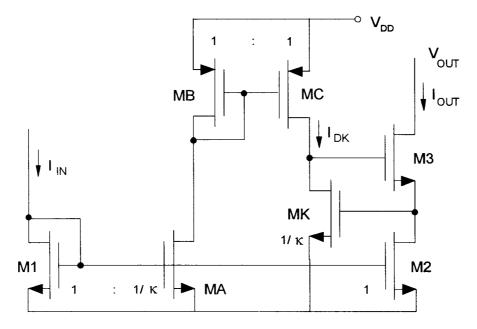

#### 2. Proposed circuit

The simplest method to achieve  $V_{DS2} = V_{GS2}$  is to choose  $M_K$  matched with  $M_1$  and set  $I_K = I_{IN}$ . Then  $I_K$  is no longer an independent current source but dependent on  $I_{IN}$ . (To distinguish between the dependent current of the new circuit and constant source current  $I_K$  of the CAFCCM, the dependent current of the new circuit will be called  $I_{DK}$ ). Since  $V_{DS2}$  need not be accurately equal to  $V_{GS2}$ ,  $I_{DK}$  can be obtained from  $I_{IN}$  by using simple current mirrors.  $I_{DK}$  can also be chosen equal to  $I_{IN}/\kappa$ , where  $\kappa > 1$ ; provided that  $(W/L)_K = (W/L)_A = (W/L)_1/\kappa$ , where  $W \times L$  is the area of the chip. This will be an advantage for keeping power consumption lower and chip area smaller.

Small-signal output impedance for the CAFCCM and for the new circuit (when  $I_{DK} = I_K$  is assumed) can be approximated as (Yang and Allstot 1990)

$$r_{o} = r_{d2}(g_{m3}r_{d3})(g_{mK}r_{dK})$$

(1)

Equation (1) shows that output impedance  $r_o$  is directly proportional to  $g_{mK}r_{dK}$ , which can be expressed as

$$g_{mK}r_{dK} = \mu_{n}C_{ox}\left(\frac{W}{L}\right)_{K}\frac{(V_{GSK} - V_{TN})}{\lambda_{N}I_{DK}}$$

(2)

if  $r_{dK} = 1/\lambda_N I_{DK}$  is assumed. Here,  $\lambda_N$  is the channel length modulation parameter for the n-channel MOSFETs. It can be observed from (2) that, when  $(W/L)_K$  and  $I_{DK}$  are decreased by a factor  $\kappa$  to reduce power consumption and chip area, there can be only a slight change in the output impedance practically (no change at all, theoretically).

The resulting circuit is given in Fig. 2. Although diminishing the devices increases the errors in matching of  $M_A$  and  $M_K$ , since  $I_{DK} = I_{IN} / \kappa$  equality need not be precisely achieved (that is why simple current mirrors are preferred for obtaining  $I_{DK}$  from  $I_{IN}$ ), this will not affect the circuit's performance significantly. When designing the circuit, aspect ratios should be chosen such that  $M_C$  remains in saturation for the maximum possible input current to be handled by the circuit. In a circuit employing the new current mirror,  $I_{DK} = I_{IN} / \kappa$  can be obtained more easily if  $I_{IN}$ can be reflected from the device supplying it; thus,  $M_A$  and  $M_B$  can be eliminated, decreasing chip area and power consumption further.

The transfer error  $\varepsilon$  (which depends on I<sub>IN</sub>) can be extracted from the following equations. (For simplicity of the analysis,  $\kappa = 1$  is assumed. Therefore,  $(W/L)_1 = (W/L)_K = (W/L)_A$ ; thus  $\beta_1 = \beta_K$ , where  $\beta_{1,K} = (W/L)_{1,K} \mu_n C_{ox}$ . In the equations,  $\beta_N$  is used to represent both  $\beta_1$  and  $\beta_K$ .) Here,  $\varepsilon$  is the current transfer

A. Zeki and H. Kuntman

Figure 2. Proposed active-feedback current mirror.

error from input to output. The approximations in (3) are made using the general approximation approach that, 'if  $x \ll 1$  and  $y \ll 1$ , then  $(1 + x)/(1 + y) \approx (1 + x)(1 - y) = 1 + x - y + xy \approx 1 + x - y'$ , where  $x = \lambda_N V_{GSK}$  and  $y = \lambda_N V_{GSI}$ .

$$\frac{I_{D2}}{I_{D1}} = 1 + \varepsilon = \frac{1 + \lambda_N V_{GSK}}{1 + \lambda_N V_{GS1}}$$

$$\approx (1 + \lambda_N V_{GSK})(1 - \lambda_N V_{GS1})$$

$$= 1 + \lambda_N (V_{GSK} - V_{GS1}) + \lambda_N^2 V_{GSK} V_{GS1}$$

$$\approx 1 + \lambda_N (V_{GSK} - V_{GS1})$$

(3)

The voltage difference  $V_{GSK}\mbox{ - } V_{GS1}$  can be expressed as

$$\mathbf{V}_{\text{GSK}} - \mathbf{V}_{\text{GS1}} = \left( \left( \frac{2\mathbf{I}_{\text{DK}}}{\beta_{\text{N}}} \right)^{1/2} + \mathbf{V}_{\text{TN}} \right) - \left( \left( \frac{2\mathbf{I}_{\text{D1}}}{\beta_{\text{N}}} \right)^{1/2} + \mathbf{V}_{\text{TN}} \right)$$

$$= \left( \frac{2}{\beta_{\text{N}}} \right)^{1/2} (\mathbf{I}_{\text{DK}}^{1/2} - \mathbf{I}_{\text{D1}}^{1/2})$$

(4)

By using (3) and (4), the transfer error can be extracted as

$$\varepsilon = \lambda_{\rm N} \left(\frac{2}{\beta_{\rm N}}\right)^{1/2} (\mathbf{I}_{\rm DK}^{1/2} - \mathbf{I}_{\rm D1}^{1/2}) = \lambda_{\rm N} \left(\frac{2}{\beta_{\rm N}}\right)^{1/2} (\left[\mathbf{I}_{\rm D1}(1+\varepsilon_{\rm K})\right]^{/2} - \mathbf{I}_{\rm D1}^{1/2})$$

$$= \lambda_{\rm N} \left(\frac{2\mathbf{I}_{\rm D1}}{\beta_{\rm N}}\right)^{1/2} ((1+\varepsilon_{\rm K})^{1/2} - 1)$$

(5)

where  $\varepsilon_K$  is the error in  $I_{DK},$  which is defined in the following equation, in a

similar way as  $\varepsilon$ :

$$\frac{\mathbf{I}_{\mathrm{DK}}}{\mathbf{I}_{\mathrm{D1}}} = \frac{1 + \lambda_{\mathrm{N}} \mathbf{V}_{\mathrm{DSK}}}{1 + \lambda_{\mathrm{N}} \mathbf{V}_{\mathrm{GS1}}} = 1 + \varepsilon_{\mathrm{K}}$$

(6)

Using the approximation approach  $(1 + x)^{1/2} \approx 1 + x/2$  for  $x \ll 1'$ , where  $x = \varepsilon_K$ , the transfer error expression can be simplified as

$$\varepsilon \approx \left(\frac{\mathbf{I}_{\mathrm{D1}}}{2\beta_{\mathrm{N}}}\right)^{1/2} \lambda_{\mathrm{N}} \varepsilon_{\mathrm{K}} \tag{7}$$

It can be easily observed from (6) and (7) that the transfer error of the new circuit can be kept very low, if  $\varepsilon_{\rm K}$  is low enough, i.e. if  $I_{\rm DK} = I_{\rm D1}$  is achieved satisfactorily. On the other hand,  $\varepsilon_{\rm K}$  may be very high in the CAFCCM because of the difference between  $I_{\rm D1}$  and constant source current  $I_{\rm K}$ , increasing the overall error  $\varepsilon$ .

Besides transfer accuracy, the new circuit has some other advantages over CAFCCM, which can be utilized by making a proper design:

- (i) there is no need for additional biasing circuitry to obtain a constant current  $I_{\rm K}$ ;

- (ii) power consumption is  $V_{DD}(2I_{IN} + I_K)$  for CAFCCM and  $2V_{DD}I_{IN}(1 + 1/\kappa)$  for the new circuit, which means that, by choosing  $\kappa > 1$ , power consumption of the new circuit can be kept lower than that of the CAFCCM; especially for input current levels lower than  $I_K$ ;

- (iii) chip area can be kept very near to that of the CAFCCM, by choosing higher  $\kappa$  values.

Additionally, if circuitry supplying  $I_K$  is accounted for in CAFCCM, it is possible to keep the new circuit's chip area smaller and power consumption significantly lower than those of CAFCCM.

Some words must be added about output impedance properties of the CAFCCM and the proposed current mirror in order to find out whether the proposed structure achieves the high output impedance performance of CAFCCM adequately or not.

Equation (1) can be expressed to obtain the dependency of small signal output impedance on  $I_{IN}$  and  $I_K$ . By choosing  $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_K$  and neglecting the body effect for M3 for simplicity, one obtains

$$r_{o} = \frac{2\beta_{N}}{\lambda_{N}^{3} I_{IN}^{3/2} I_{K}^{1/2}}$$

(8)

for the CAFCCM, where  $\beta_N$  and  $\lambda_N$  are common parameters for M1, M2, M3 and MK. For the proposed current mirror,  $I_K$  must be replaced with  $I_{IN}$ . This means that, for input current levels lower than  $I_K$ , the new circuit's output impedance is better than that of the CAFCCM; while for  $I_{IN} > I_K$ , the CAFCCM has a higher output impedance. However, since the  $r_o$  difference is via square root of a ratio  $I_{IN} / I_K$ , the advantage and disadvantage of the new circuit over CAFCCM is not very important, unless  $I_{IN}$  is far higher or lower than  $I_K$  of the CAFCCM. For example, even if  $I_{IN}$  is 100 times higher or lower than  $I_K$ , the difference in  $r_o$  is only a factor of 10. Since output impedance for these structures is quite high, this extreme case generally does not cause a serious performance shift when the current mirror is used in a stage where high output impedance of the current mirror is demanded.

339

| PMOS model parameters                                                                                  |                                                                                                                                                                                                             | NMOS model parameters                                                                                        |                                                                                                        |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| $VTO = -0.8TOX = 400 \times 10^{-10}NSUB = 4 \times 10^{15}XJ = 0.21ULD = 0.45UUO = 300VMAX = 3 × 104$ | $\begin{array}{l} \text{GAMMA} = 0.46\\ \text{NFS} = 1.68 \times 10^{11}\\ \text{CGSO} = 124P\\ \text{CGDO} = 0.124N\\ \text{CGBO} = 40.3P\\ \text{PB} = 0.6\\ \text{CJ} = 1.83 \times 10^{-4} \end{array}$ | $VTO = 0.99TOX = 400 \times 10^{-10}NSUB = 7 \times 10^{15}XJ = 0.18ULD = 0.341UUO = 710VMAX = 1.5 × 10^{5}$ | $GAMMA = 0.65NFS = 2.4 \times 10^{11}CGSO = 87PCGDO = 87PCGBO = 27.9PPB = 0.6CJ = 1.78 \times 10^{-4}$ |

| DELTA = 0.75<br>THETA = 0.4<br>ETA = 0.15<br>KAPPA = 1.5<br>TPG = -1                                   | $JS = 3.46 \times 10^{-8}$<br>MJ = 0.526<br>CJSW = 229P<br>MJSW = 0.172<br>LAMBDA = 0.01                                                                                                                    | DELTA = 0.3<br>THETA = 0.15<br>ETA = 0.15<br>KAPPA = 0.6<br>TPG = 1                                          | $JS = 8.2 \times 10^{-8}$<br>MJ = 0.481<br>CJSW = 358P<br>MJSW = 0.218<br>LAMBDA = 0.02                |

Table 1. YİTAL 3µm process SPICE model parameters for the PMOS and NMOS transistors.

## 3. Simulation results

SPICE simulations were carried out for the CAFCCM and the new circuit, using the model parameters of TÜBİTAK-YİTAL'S  $3\mu$ m n-well CMOS process, also given in Table 1.  $V_{DD} = 5 V$  and all channel lengths are  $5\mu$ m. Bulks are connected to  $V_{DD}$  for the p-channel and to the ground for the n-channel MOSFETs.  $W_1 = W_2 = W_3 = 150 \mu$ m for both circuits. (Note that M<sub>3</sub> need not match with M<sub>1</sub> or M<sub>2</sub>; it can be made wider to increase output dynamic range further.) W<sub>K</sub> is  $150 \mu$ m for the CAFCCM, while  $W_A = W_K = 15 \mu$ m in the new circuit to achieve  $\kappa = 10$ . Finally,  $W_B = W_C = 25 \mu$ m. It is worth mentioning that small signal output impedance values for both circuits obtained by simulation were almost equal for  $I_{IN} = I_K = 250 \mu$ A.

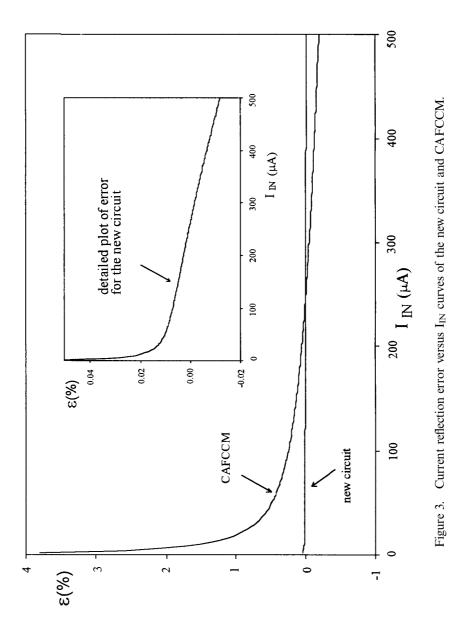

In Fig. 3, transfer error versus  $I_{IN}$  curves for the new circuit and the CAFCCM ( $I_K = 250 \,\mu A$ ) are plotted. It can be observed that the transfer accuracy for the new circuit is higher than that of the CAFCCM. For low input current levels, the new circuit's performance is very high, while the CAFCCM fails to operate accurately. The CAFCCM operates accurately only when  $I_{IN}$  is around  $250 \,\mu A$  (i.e. around  $I_K$ ), which is an expected result. It should be emphasized that the error source in CAFCCM is mainly channel length modulation, while in the new circuit it is mainly transistor mismatches, due to the elimination of channel length modulation effects by the proposed method.

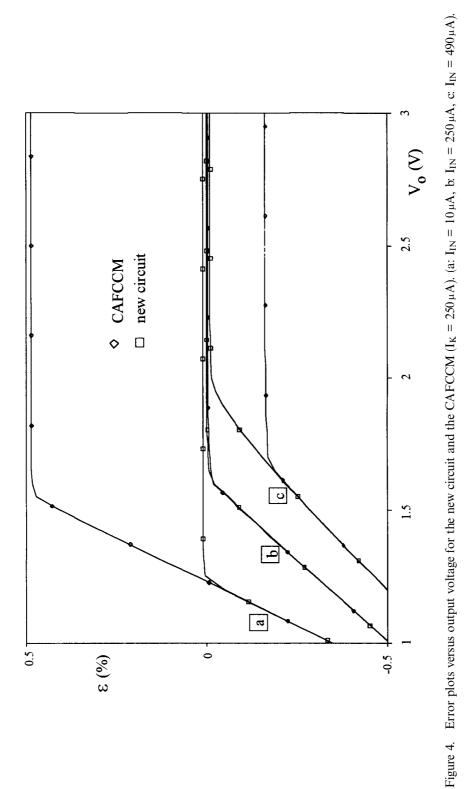

In Fig. 4, transfer error versus output voltage curves are plotted for three  $I_{IN}$  values (10  $\mu$ A, 250  $\mu$ A and 490  $\mu$ A) to compare output swing limitations of the CAFCCM and the new circuit.  $I_K$  is 250  $\mu$ A for the CAFCCM.

For  $I_{IN} = 250 \,\mu A = I_K$  (case b), it is clear that both circuits act the same way, which is an expected result.

For  $I_{IN} = 10 \,\mu\text{A} < I_K$  (case a), error and output swing limitations of the new circuit are much lower than those of the CAFCCM. This is due to the difference between  $V_{DS2}$  and  $V_{DS1} = V_{GS1}$ .

For  $I_{IN} = 490 \,\mu A > I_K$  (case c), the error for the new circuit is still lower than that of the CAFCCM, but it seems that output swing is worse for the new circuit, when only the breakpoints are compared. However, this comparison based on the 'breakpoint' criteria is not a fair one. The CAFCCM's breakpoint voltage is lower, at the cost of its transfer accuracy. A more appropriate comparison can be made by

defining the output voltage limit for the new circuit as the point where transfer accuracy drops to the transfer accuracy value of the CAFCCM. This proves output swing performance of the new circuit, for this case, is not worse but practically the same as that of the CAFCCM. Thus, output swing limitations for the new circuit is in all cases better than (and for the worst case, the same as) that of the CAFCCM.

#### 4. Conclusion

An improved active-feedback CMOS cascode current mirror is introduced in this paper. It is verified, by SPICE simulations, that the new current mirror has a very accurate reflection ratio, while achieving the same high output impedance property of an equivalent conventional active-feedback cascode current mirror and wider (or, in the worst case, the same) output dynamic range. The current mirror can accurately reflect currents of a wide range of magnitude, which can be determined by design. The new structure does not need an additional constant current source as the CAFCCM does. The power consumption can be kept lower than that of the CAFCCM, especially for input currents lower than  $I_K$ . Chip area is almost equal to that of the CAFCCM and can be kept even smaller when it is employed in a circuit. The new circuit can be used in high precision analogue integrated circuits, especially in structures where current-mode techniques are used. With its optimal output dynamic range, it is also suitable for precise low voltage analogue integrated circuit design.

### References

- PALMISANO, G., PALUMBO, G., and PENNISI, S., 1995, High linearity CMOS output stage. *IEE Electronics Letters*, **31**, 789–790.

- SÄCKINGER, E., and GUGGENBÜHL, W., 1990, A high-swing, high impedance MOS cascode circuit. *IEEE Journal of Solid-state Circuits*, **25**, 289–298.

- YANG, H. C., and Allstot, D. J., 1990, An active-feedback cascode current source. *IEEE Transactions on Circuits and Systems*, 37, 644–646.

- ZEKİ, A., and KUNTMAN, H., 1995, New MOSFET model suitable for analogue IC analysis. International Journal of Electronics, 78, 247–260.

- ZEKİ, A., and KUNTMAN, H., 1996, A novel CMOS OTA structure suitable for OTA-C filters. International Conference on Microelectronics (ICM96), Cairo, Egypt, 7–10 December (accepted for aural presentation).